# ACCELERATING SCIENCE WITH DIRECTIVE-BASED PROGRAMMING ON HETEROGENEOUS MACHINES AND FUTURE TECHNOLOGIES

by

JACOB B. LAMBERT

### A DISSERTATION

Presented to the Department of Computer and Information Science and the Division of Graduate Studies of the University of Oregon in partial fulfillment of the requirements for the degree of Doctor of Philosophy

September 2021

### DISSERTATION APPROVAL PAGE

Student: Jacob B. Lambert

Title: Accelerating Science with Directive-Based Programming on Heterogeneous Machines and Future Technologies

This dissertation has been accepted and approved in partial fulfillment of the requirements for the Doctor of Philosophy degree in the Department of Computer and Information Science by:

Allen Malony Chair

Boyana R. Norris Core Member Hank R. Childs Core Member Seyong Lee Core Member

Josef Dufek Institutional Representative

and

Andy Karduna Interim Vice Provost for Graduate Studies

Original approval signatures are on file with the University of Oregon Division of Graduate Studies.

Degree awarded September 2021

### © 2021 Jacob B. Lambert

This work, including text and images of this document but not including supplemental files (for example, not including software code and data), is licensed under a Creative Commons

Attribution-ShareAlike 4.0 International License.

#### DISSERTATION ABSTRACT

Jacob B. Lambert

Doctor of Philosophy

Department of Computer and Information Science

September 2021

Title: Accelerating Science with Directive-Based Programming on Heterogeneous Machines and Future Technologies

Accelerator-based heterogeneous computing has become the de facto standard in contemporary high-performance machines, including upcoming exascale machines. These heterogeneous platforms have been instrumental to the development of computation-based science over the past several years. However, this specialization of hardware has also led to a specialization of associated heterogeneous programming models that are often intimidating to scientific programmers and that may not be portable or transferable between different platforms. Directive-based programming offers one high-level alternative to specialized code, but also introduces its own set of challenges. Many accelerators, like FPGAs, may not support a directive-based approach, and others like GPUs and CPUs may selectively support standards. In this dissertation we perform the necessary research required to further enable directive-based computing to consistently accelerate science on heterogeneous platforms. This research takes the form of three major projects: (1) an OpenACC-to-FPGA framework developed to bring FPGAs under the umbrella of directive-based computing, (2) an OpenACC and OpenMP interoperable framework designed to improve the portability and performance of directive-based standards across different platforms, and (3) an

exploration of exascale-intended platforms with directive-based applications. This dissertation includes previously published and co-authored material, as well as unpublished co-authored material.

### CURRICULUM VITAE

NAME OF AUTHOR: Jacob B. Lambert

### GRADUATE AND UNDERGRADUATE SCHOOLS ATTENDED:

University of Oregon, Eugene, OR, USA University of Tennessee, Knoxville, TN, USA Technical University of Denmark, Kongens Lyngby, Denmark

### DEGREES AWARDED:

Doctor of Philosophy, Computer and Information Science, 2021, University of Oregon

Bachelor of Arts, Computer Science, 2015, University of Tennessee

### AREAS OF SPECIAL INTEREST:

High Performance Computing Heterogeneous Programming Models Computational Science

### PROFESSIONAL EXPERIENCE:

Research Collaborator/Affiliate, Oak Ridge National Laboratory Future Technologies Group, 2016-present, Advisor: Seyong Lee, Jeffrey Vetter

Graduate Teaching Assistant, University of Oregon, Advisor: Allen Malony, 2015, 2016

Research Assistant, Oak Ridge National Lab Electrical and Electronics Systems Research Division, Advisor: Mark Buckner, 2013

Student Researcher, Eco-Informatics Summer Institute (EISI), 2013

Student Researcher, National Institute for Mathematical Biological Synthesis (NIMBioS), 2013

# GRANTS, AWARDS AND HONORS:

Research Collaboration Grant, Oak Ridge National Laboratory, 2019

### PUBLICATIONS:

- Lambert, J., Lee, S., Vetter, J. S., and Malony, A. D. (2021). Optimization with the OpenACC-to-FPGA Framework on the Arria 10 and Stratix 10 FPGAs. *Journal of Parallel Computing (PARCO)*

- Cabrera, A., Young, A., and Lambert, J. (2021). Towards Evaluating High-Level Synthesis Portability and Performance Between Intel and Xilinx FPGAs. *International Workshop on OpenCL and SYCL (IWOCL)*

- Lambert, J., Lee, S., Vetter, J. S., and Malony, A. D. (2020). CCAMP: An Integrated Translation and Optimization Framework for OpenACC and OpenMP. *International Conference on Supercomputing (SC)*.

- Lambert, J., Lee, S., Vetter, J. S., and Malony, A. (2020). In-depth optimization with the OpenACC-to-FPGA framework on an Arria 10 FPGA. *International Parallel and Distributed Processing Symposium Workshops (IPDPSW)* (pp. 460-470). IEEE.

- Lambert, J., Lee, S., Vetter, J. S., and Malony, A. D. (2019). CCAMP: OpenMP and OpenACC Interoperable Framework. *European Conference on Parallel Processing (EuroPAR)*

- Lambert, J., Lee, S., Kim, J., Vetter, J. S., and Malony, A. D. (2018). Directive-Based, High-Level Programming and Optimizations for High-Performance Computing with FPGAs. *International Conference on Supercomputing (ICS)* (pp. 160-171). ACM.

- Lee, S., Lambert, J., Kim, J., Vetter, J. S., and Malony, A. D. (2018). OpenACC to FPGA: A Directive-Based High-Level Programming Framework for High-Performance Reconfigurable Computing. The International Conference for High Performance Computing, Networking, Storage, and Analysis (SC) (Poster)

### ACKNOWLEDGEMENTS

I want to thank Allen Malony for his unwavering support, for inspiring me to pursue high-performance computing, and for guiding me through this process of learning. I also want to thank Hank Childs and Boyana Norris for serving not only on my dissertation committee, but also for advising all of my graduate milestones. For their support throughout my graduate studies, I want to thank the ORNL Future Technologies Group, including Jeffrey Vetter, Joel Denny, and especially Seyong Lee. As the mastermind of OpenARC, Dr. Lee laid out the groundwork that made the research in this dissertation possible, and I value everything I have learned from him over the past five years. The research in this dissertation would have been impossible without Philip Roth, Steve Moulton, and Erik Keever's relentless support in maintaining the software and hardware environments I worked with. I also want to thank the program coordinators and administrative assistants that contributed to my success as a student and intern: Cheri Smith, Liz Herbert, Donna Wilkerson, Tara Hall, and Charlotte Wise, and Vickie Braga. Finally I want to thank my graduate student peers, including Jonathan Brophy, Mohammad Monil, Sam Pollard, Chad Wood, and so many others, whose support and companionship have made this graduate experience even more rewarding.

To my father, who taught me the value of integrity and commitment; my mother, who sparked my love for science; and my partner, for all of the love and support during this adventure

# TABLE OF CONTENTS

| Cl | naptei | ſ      |                                                                     | Page |

|----|--------|--------|---------------------------------------------------------------------|------|

| I. | INT    | RODUC  | CTION, BACKGROUND, AND MOTIVATION                                   | . 1  |

|    | 1.1.   | Histor | y of Heterogeneous Computing                                        | . 7  |

|    |        | 1.1.1. | Distributed Heterogeneous Systems                                   | . 8  |

|    |        | 1.1.2. | Multicore, Manycore, and Accelerator-based<br>Heterogeneous Systems | . 15 |

|    | 1.2.   | Hetero | ogeneous Programming Models                                         | . 18 |

|    |        | 1.2.1. | CUDA                                                                | . 18 |

|    |        | 1.2.2. | OpenCL                                                              | . 20 |

|    |        | 1.2.3. | HIP                                                                 | . 22 |

|    |        | 1.2.4. | OpenACC                                                             | . 23 |

|    |        | 1.2.5. | OpenMP                                                              | . 24 |

|    |        | 1.2.6. | Other Modern Programming Models                                     | . 26 |

|    |        |        | 1.2.6.1. Kokkos                                                     | . 27 |

|    |        |        | 1.2.6.2. Raja                                                       | . 27 |

|    |        |        | 1.2.6.3. SYCL, DPC++, and OneAPI                                    | . 28 |

|    |        |        | 1.2.6.4. Legion                                                     | . 29 |

|    |        |        | 1.2.6.5. HPX                                                        | . 30 |

|    |        |        | 1.2.6.6. C++                                                        | . 30 |

|    |        |        | 1.2.6.7. Domain Specific Languages                                  | . 31 |

|    | 1.3.   | Hetero | ogeneous Compiler Frameworks                                        | . 34 |

|    |        | 1.3.1. | Vendor-supported Compilers                                          | . 34 |

|    |        |        | 1.3.1.1. NVCC                                                       | . 35 |

|    |        |        | 1.3.1.2. PGI                                                        |      |

| Chapter |                    |           |                                     | Pa | ıge |

|---------|--------------------|-----------|-------------------------------------|----|-----|

|         |                    | 1.3.1.3.  | AMD                                 |    | 36  |

|         |                    | 1.3.1.4.  | Intel                               |    | 37  |

|         | 1.3.2.             | Open-sou  | ırce Compilers                      |    | 37  |

|         |                    | 1.3.2.1.  | LLVM, Clang, and MLIR               |    | 39  |

|         |                    | 1.3.2.2.  | GNU C/C++                           |    | 41  |

|         | 1.3.3.             | Academi   | c, Research, and Custom Compilers   |    | 41  |

|         |                    | 1.3.3.1.  | ROSE                                |    | 42  |

|         |                    | 1.3.3.2.  | OpenUH                              |    | 42  |

|         |                    | 1.3.3.3.  | Omni                                |    | 42  |

|         |                    | 1.3.3.4.  | OmpSs                               |    | 43  |

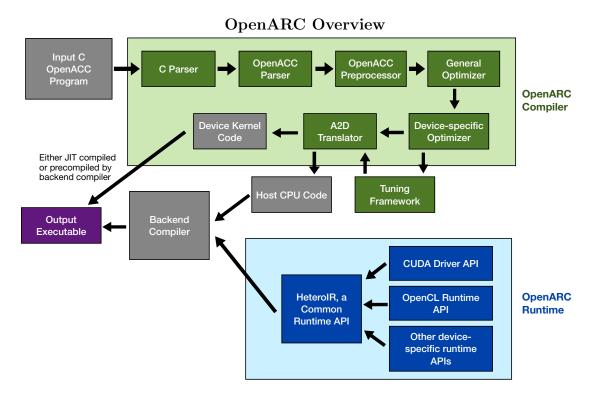

|         |                    | 1.3.3.5.  | OpenARC                             |    | 44  |

|         |                    | 1.3.3.6.  | HPVM                                |    | 45  |

| 1.4.    | Hetero             | geneous E | Benchmark Suites                    |    | 46  |

|         | 1.4.1.             | Rodinia   |                                     |    | 46  |

|         | 1.4.2.             | SPEC A    | ccel                                |    | 46  |

|         | 1.4.3.             | Other He  | eterogeneous Benchmark Suites       |    | 47  |

|         |                    |           | PROGRAMMING AND                     |    |     |

|         |                    |           | OR HIGH-PERFORMANCE<br>FPGAS        |    | 51  |

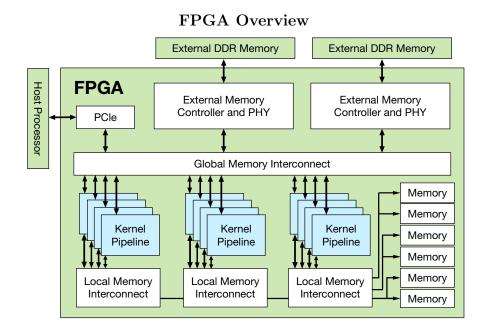

| 2.1.    | Backgr             | ound on l | FPGAs as Heterogeneous Accelerators |    | 52  |

|         | 2.1.1.             | FPGA H    | ardware                             |    | 53  |

|         | 2.1.2.             | Tradition | nal FPGA Programming Approaches     |    | 53  |

|         | 2.1.3.             | Contemp   | oorary FPGA Programming Models      |    | 54  |

|         |                    | 2.1.3.1.  | OpenCL                              |    | 54  |

|         |                    | 2.1.3.2.  | OpenACC                             |    | 56  |

| 2.2.    | The O <sub>1</sub> | oenACC-t  | to-FPGA Framework                   |    | 57  |

| Chapter | •      |           |                                         | Р | age |

|---------|--------|-----------|-----------------------------------------|---|-----|

|         | 2.2.1. | Impleme   | entation in OpenARC                     |   | 59  |

|         | 2.2.2. | Automa    | tic Optimizations                       |   | 60  |

|         |        | 2.2.2.1.  | Dynamic Memory Transfer Alignment       |   | 60  |

|         |        | 2.2.2.2.  | Boundary Check Elimination              |   | 61  |

|         |        | 2.2.2.3.  | Branch-Variant Code Motion Optimization |   | 62  |

|         | 2.2.3. | Re-purp   | osed Directives                         |   | 65  |

|         |        | 2.2.3.1.  | Single Work-Item Optimization           |   | 65  |

|         |        | 2.2.3.2.  | Collapse Optimization                   |   | 67  |

|         |        | 2.2.3.3.  | Reduction Optimization                  |   | 69  |

|         | 2.2.4. | Directive | e Extensions                            |   | 74  |

|         |        | 2.2.4.1.  | Kernel Vectorization Directive          |   | 74  |

|         |        | 2.2.4.2.  | Compute Unit Replication Directive      |   | 75  |

|         |        | 2.2.4.3.  | Channels Directive                      |   | 75  |

|         |        | 2.2.4.4.  | Sliding Window Directive                |   | 76  |

| 2.3.    | Experi | imental S | etup for FPGA Platforms                 |   | 84  |

|         | 2.3.1. | Benchma   | arks                                    |   | 84  |

|         |        | 2.3.1.1.  | Sobel                                   |   | 86  |

|         |        | 2.3.1.2.  | FD3D                                    |   | 86  |

|         |        | 2.3.1.3.  | HotSpot                                 |   | 87  |

|         |        | 2.3.1.4.  | SRAD                                    |   | 87  |

|         |        | 2.3.1.5.  | NW                                      |   | 87  |

|         |        | 2.3.1.6.  | Pathfinder                              |   | 87  |

|         |        | 2.3.1.7.  | CFD                                     |   | 88  |

|         |        | 2.3.1.8.  | Jacobi                                  |   | 88  |

|         |        | 2.3.1.9.  | Matmul                                  |   | 88  |

| Chapter |         |                                                            | F | age |

|---------|---------|------------------------------------------------------------|---|-----|

|         |         | 2.3.1.10. LULESH                                           |   | 88  |

|         | 2.3.2.  | FPGA Hardware Platforms                                    |   | 88  |

|         | 2.3.3.  | FPGA Software Platforms                                    |   | 90  |

|         | 2.3.4.  | GPU and CPU Comparison Platforms                           |   | 91  |

| 2.4.    | Intel S | Stratix V Evaluations                                      |   | 91  |

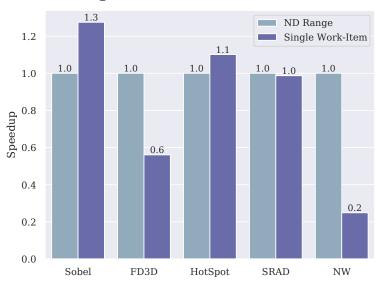

|         | 2.4.1.  | Single Work-Item Evaluation                                |   | 92  |

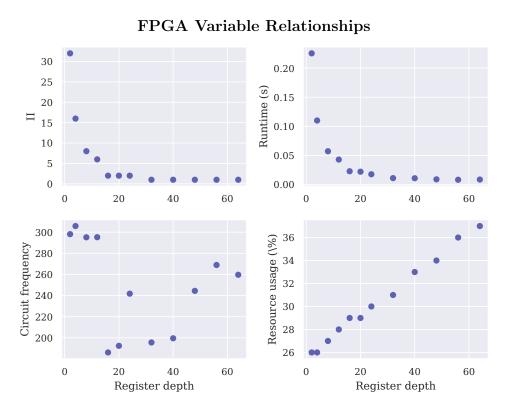

|         | 2.4.2.  | Collapse Evaluation                                        |   | 92  |

|         | 2.4.3.  | Reduction Evaluation                                       |   | 93  |

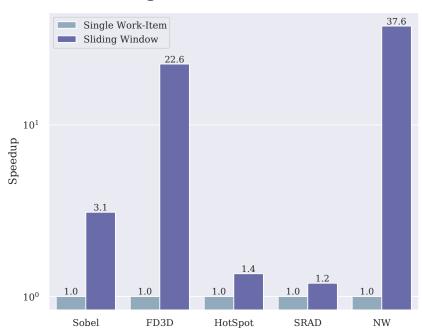

|         | 2.4.4.  | Sliding Window Evaluation                                  |   | 96  |

|         |         | 2.4.4.1. Basic Sliding Window                              |   | 96  |

|         |         | 2.4.4.2. Sliding Window with Loop Unrolling                |   | 98  |

|         | 2.4.5.  | Branch-Variant Code Motion Evaluation                      |   | 100 |

|         | 2.4.6.  | OpenACC and OpenCL Performance Comparison                  | • | 101 |

|         | 2.4.7.  | Performance and Power Comparisons of FPGAs, GPUs, and CPUs | • | 103 |

| 2.5.    | Intel A | Arria 10 and Stratix 10 Evaluations                        |   | 103 |

|         | 2.5.1.  | Sobel Holistic Evaluation                                  |   | 105 |

|         |         | 2.5.1.1. HotSpot                                           |   | 107 |

|         | 2.5.2.  | SRAD Holistic Evaluation                                   |   | 109 |

|         | 2.5.3.  | MatMul Holistic Evaluation                                 |   | 111 |

|         | 2.5.4.  | Jacobi Holistic Evaluation                                 |   | 114 |

|         | 2.5.5.  | Resource Usage Evaluation                                  |   | 115 |

|         |         | 2.5.5.1. SRAD Resource Evaluation                          |   | 116 |

|         |         | 2.5.5.2. Jacobi Resource Evaluation                        |   | 117 |

|         | 2.5.6.  | Compilation Times                                          |   | 119 |

|         | 2.5.7.  | Performance Portability                                    |   | 121 |

| Chapter | ſ       |                                                              | Page  |

|---------|---------|--------------------------------------------------------------|-------|

|         | 2.5.8.  | LULESH Initial Evaluation                                    | . 121 |

| 2.6.    | Intel a | and Xilinx OpenCL Portability Study                          | . 124 |

|         | 2.6.1.  | Porting Intel Applications to Xilinx Hardware                | . 126 |

|         |         | 2.6.1.1. Loop Unrolling                                      | . 127 |

|         |         | 2.6.1.2. Shift Registers                                     | . 128 |

|         | 2.6.2.  | Minimum Modification Porting Evaluation                      | . 129 |

|         |         | 2.6.2.1. Pathfinder Porting and Evaluation                   | . 129 |

|         |         | 2.6.2.2. CFD Porting and Evaluation                          | . 131 |

|         |         | 2.6.2.3. SRAD Porting and Evaluation                         | . 132 |

|         |         | 2.6.2.4. HotSpot Porting and Evaluation                      | . 134 |

| 2.7.    | Direct  | ive-based FPGA Programming: Related Works                    | . 135 |

| 2.8.    | Direct  | ive-based FPGA Programming: Conclusions                      | . 136 |

|         |         | RATED TRANSLATION AND OPTIMIZATION RK FOR OPENMP AND OPENACC | . 140 |

| 3.1.    | OpenN   | MP and OpenACC Interoperable Framework: Introduction         | . 140 |

| 3.2.    | CCAN    | MP: Background                                               | . 143 |

|         | 3.2.1.  | OpenACC and OpenMP                                           | . 143 |

|         | 3.2.2.  | OpenARC                                                      | . 144 |

| 3.3.    | CCAN    | MP: Automated Translation between OpenMP and OpenACC         | . 145 |

|         | 3.3.1.  | OpenMP 4+ to OpenACC                                         | . 146 |

|         | 3.3.2.  | OpenACC to OpenMP 4+                                         | . 148 |

| 3.4.    | CCAN    | MP: Automated Optimization of OpenMP and OpenACC             | . 149 |

|         | 3.4.1.  | Extracting Parallelism                                       | . 150 |

|         | 3.4.2.  | OpenMP Mapping on CPUs                                       | . 153 |

|         | 3.4.3.  | OpenMP Mapping on GPUs                                       | . 153 |

|         | 3.4.4.  | OpenACC Mapping                                              | . 154 |

| Chapter |        |            |                                                         | ŀ | age |

|---------|--------|------------|---------------------------------------------------------|---|-----|

|         | 3.4.5. | Optimiz    | ation Code Examples                                     |   | 156 |

| 3.5.    | Evalua | ation of C | CAMP Framework                                          |   | 159 |

|         | 3.5.1. | Experim    | ental Setup of Intel, IBM, and Nvidia Platforms         |   | 159 |

|         |        | 3.5.1.1.   | Devices                                                 |   | 159 |

|         |        | 3.5.1.2.   | Compilers                                               |   | 159 |

|         |        | 3.5.1.3.   | Benchmarks                                              |   | 161 |

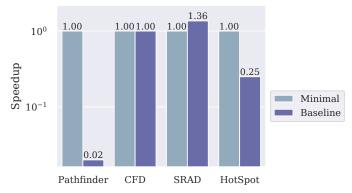

|         | 3.5.2. | Evaluati   | on of CCAMP Translation                                 |   | 163 |

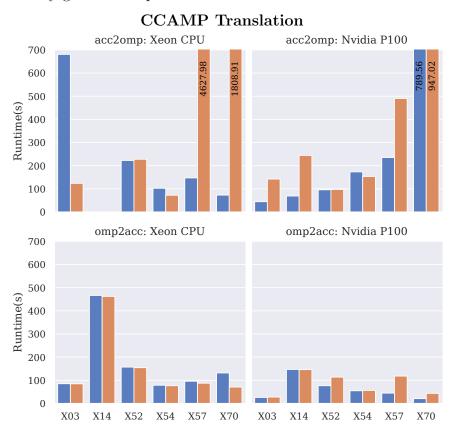

|         | 3.5.3. | Evaluati   | on of CCAMP Optimization                                |   | 165 |

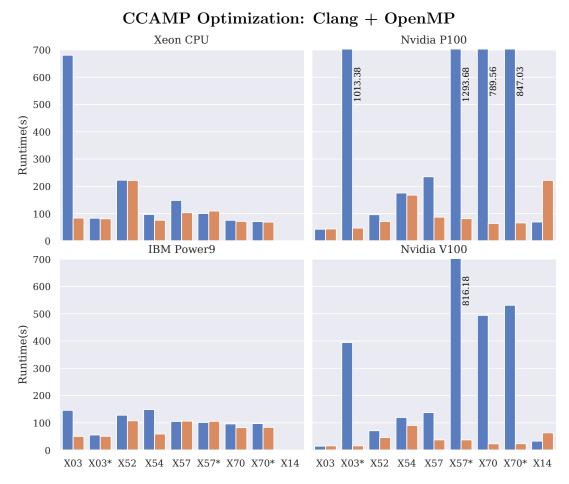

|         |        | 3.5.3.1.   | OpenMP 4+ Optimization with Clang                       |   | 165 |

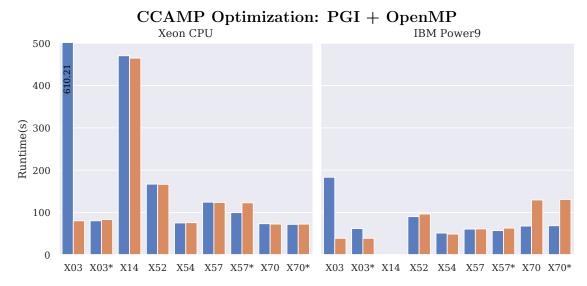

|         |        | 3.5.3.2.   | OpenMP 4+ Optimization with PGI                         |   | 167 |

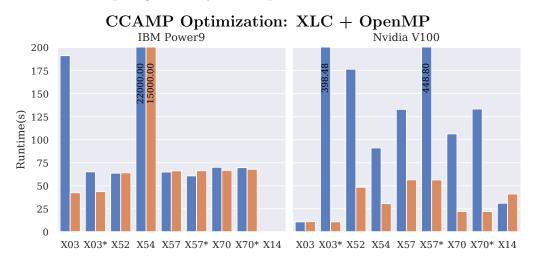

|         |        | 3.5.3.3.   | OpenMP 4+ Optimization with XLC $$                      |   | 167 |

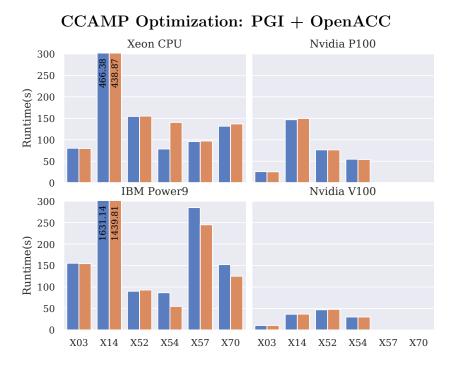

|         |        | 3.5.3.4.   | OpenACC Optimization with PGI                           |   | 168 |

|         |        | 3.5.3.5.   | Putting it Together: CCAMP Translation and Optimization |   | 169 |

|         | 3.5.4. | Addition   | nal CCAMP Evaluations                                   |   | 171 |

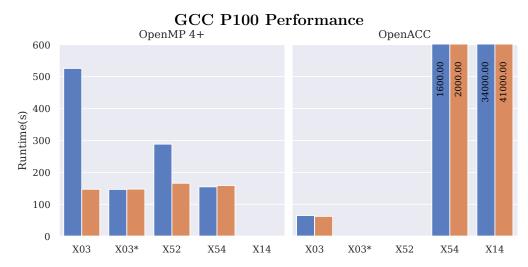

|         |        | 3.5.4.1.   | GCC: Initial Evaluation                                 |   | 171 |

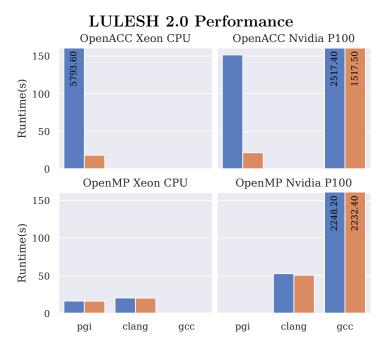

|         |        | 3.5.4.2.   | LULESH 2.0                                              |   | 172 |

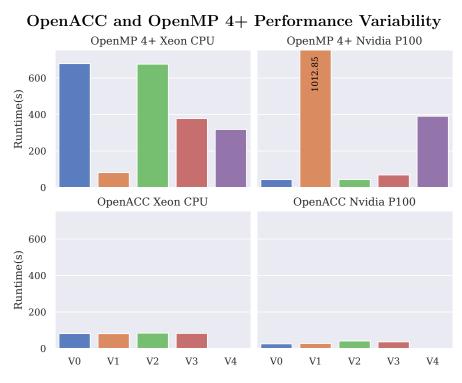

|         |        | 3.5.4.3.   | Performance Variability                                 |   | 173 |

| 3.6.    | -      |            | penACC Interoperable Framework:                         |   | 177 |

| 3.7.    | OpenN  | MP and C   | penACC Interoperable Framework: Conclusions             |   | 178 |

|         |        |            | ROGENEOUS PROGRAMMING FOR EXASCALE PLATFORMS            |   | 181 |

| 4.1.    | Explor | ation of l | Exascale Platforms: Introduction                        |   | 181 |

| 4.2.    | Exasca | ale Platfo | rms and Programming Models                              |   | 182 |

|         | 4.2.1. | Exascale   | Programming Models                                      |   | 184 |

| Chapte: | r      | Р                                                               | age |

|---------|--------|-----------------------------------------------------------------|-----|

|         |        | 4.2.1.1. OpenMP                                                 | 184 |

|         |        | 4.2.1.2. OpenACC                                                | 185 |

|         |        | 4.2.1.3. CUDA                                                   | 185 |

|         |        | 4.2.1.4. OpenCL                                                 | 186 |

|         |        | 4.2.1.5. HIP/ROCm                                               | 186 |

|         |        | 4.2.1.6. Other Notable Models                                   | 187 |

| 4.3.    | Explor | ration of Exascale Platforms: Experimental Setup                | 189 |

|         | 4.3.1. | AMD Platform                                                    | 189 |

|         | 4.3.2. | Nvidia Platform                                                 | 190 |

|         | 4.3.3. | Intel Platform                                                  | 191 |

|         | 4.3.4. | Benchmarks                                                      | 192 |

| 4.4.    |        | ation of Heterogeneous Platforms with OpenACC, ARC, and CCAMP   | 193 |

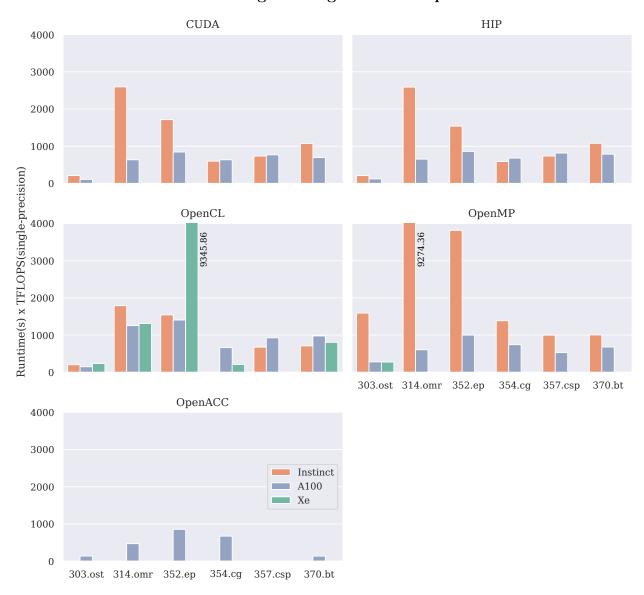

|         | 4.4.1. | Relative Performance of Each Programming Model Across Devices   | 193 |

|         | 4.4.2. | Absolute Performance of Programming Models on Each Device       | 198 |

|         | 4.4.3. | OpenMP Mappings                                                 | 202 |

|         | 4.4.4. | Intel $icpx$ and Intermediate Representations for OpenMP $$     | 204 |

|         | 4.4.5. | LLVM and Nvidia Implementation Comparison for OpenCL and OpenMP | 205 |

| 4.5.    | Explo  | ration of Exascale Platforms: Related Work                      | 207 |

| 4.6.    | Explo  | ration of Exascale Platforms: Conclusions                       | 209 |

| V. CON  | ICLUSI | ON                                                              | 212 |

| REFER   | ENCES  | SCITED                                                          | 215 |

# LIST OF FIGURES

| Figu | ire                                                                                                                                         | I | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|---|------|

| 1.   | Summary of the state of heterogeneous programming and computing                                                                             |   | 6    |

| 2.   | Re-evaluation of the state heterogeneous programming and computing.                                                                         |   | 6    |

| 3.   | Re-creation of conceptual model of heterogeneous computing                                                                                  |   | 12   |

| 4.   | Overview of OpenARC compiler framework                                                                                                      |   | 45   |

| 5.   | FPGA hardware components available through Intel OpenCL SDK for FPGAs                                                                       |   | 54   |

| 6.   | OpenACC-to-FPGA multi-threaded and pipeline-parallel approaches (Stratix V)                                                                 |   | 93   |

| 7.   | Initialization interval (II), circuit frequency, runtime, resource usage, and shift-register depth relationships (Stratix V)                |   | 95   |

| 8.   | Comparison of a single work-item and a single work-item with shift-register sliding window approach (Stratix V)                             |   | 97   |

| 9.   | Sliding window optimization with different unroll factors applied (Stratix V) $\dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$ |   | 99   |

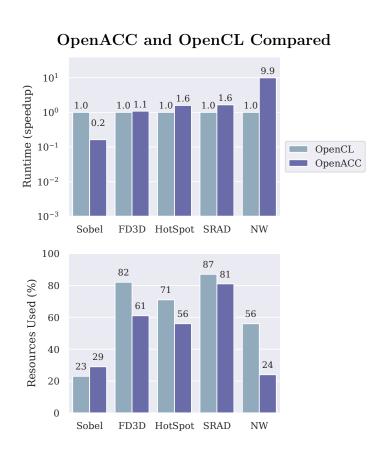

| 10.  | OpenACC and OpenCL with FPGA-specific optimizations (Stratix V)                                                                             |   | 102  |

| 11.  | Comparison of OpenMP CPU (Xeon x32) executions,<br>OpenACC GPU (K40c) executions, and OpenACC FPGA<br>(Stratix V)                           |   | 104  |

| 12.  | Runtime performance of Sobel with different FPGA-specific optimizations applied (Arria 10 and Stratix 10)                                   | • | 106  |

| 13.  | Runtime performance of HotSpot with different FPGA-specific optimizations applied (Arria 10 and Stratix 10)                                 |   | 108  |

| 14.  | Runtime performance of SRAD with different FPGA-<br>specific optimizations applied (Arria 10 and Stratix 10)                                |   | 110  |

| Figu | are                                                                                                                                            | Page  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 15.  | Runtime performance of MatMul with different FPGA-specific optimizations applied. (Arria 10 and Stratix 10)                                    | . 112 |

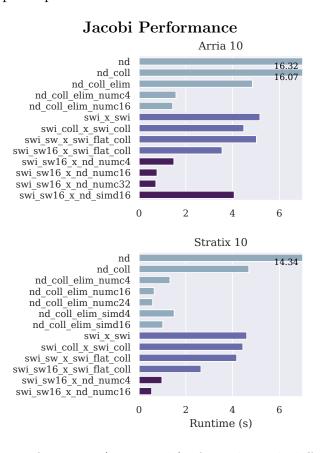

| 16.  | Runtime performance of Jacobi with different FPGA-specific optimizations applied (Arria 10 and Stratix 10)                                     | . 113 |

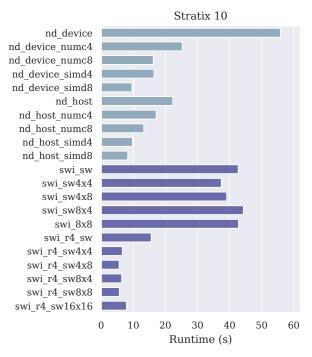

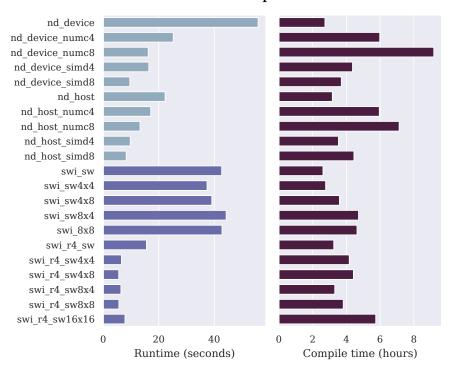

| 17.  | SRAD Runtime performance compared to compilation time (Stratix 10)                                                                             | . 120 |

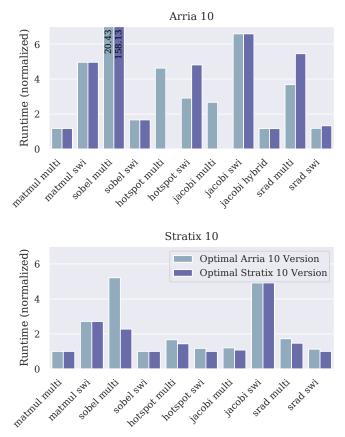

| 18.  | Performance portability evaluation (Stratix 10 and Arria 10)                                                                                   | . 122 |

| 19.  | The average percentage of peak performance achieved when executing program versions optimized for each device across the two different devices | . 122 |

| 20.  | Runtime performance of LULESH with different FPGA-specific optimizations (Stratix 10 and Arria 10)                                             | . 124 |

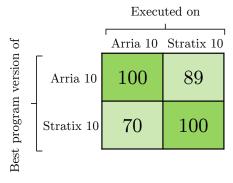

| 21.  | Performance comparison of baseline and optimized kernels (U250) $$                                                                             | . 130 |

| 22.  | Performance comparison of manually coded applications and CCAMP-translated applications                                                        | . 164 |

| 23.  | Clang + OpenMP. Run time comparison of SPEC hand-<br>optimized and CCAMP automated optimization                                                | . 166 |

| 24.  | PGI + OpenMP. Run time comparison of SPEC hand-<br>optimized and CCAMP automated optimization                                                  | . 167 |

| 25.  | XLC + OpenMP. Run time comparison of SPEC hand-<br>optimized and CCAMP automated optimization                                                  | . 168 |

| 26.  | PGI + OpenACC. Run time comparison of SPEC hand-<br>optimized and CCAMP automated optimization                                                 | . 170 |

| 27.  | GCC performance of OpenACC manual and CCAMP optimized (P100)                                                                                   | . 172 |

| 28.  | Performance of OpenACC manual and CCAMP optimized, and performance of OpenMP translated and OpenMP translated + optimized                      | . 174 |

| 29.  | Comparison of performance variability with different sets of directives between OpenMP and OpenACC                                             | . 175 |

| 30.  | Relative runtime comparison of programming models across devices                                                                               | . 194 |

| Figu | re                                                                                                 | Page  |

|------|----------------------------------------------------------------------------------------------------|-------|

| 31.  | Absolute runtime performance comparison of different programming models                            | . 199 |

| 32.  | Runtime performance comparison of different CCAMP OpenMP mappings across different architectures   | . 203 |

| 33.  | Runtime performance comparison of two OpenCL implementations and two OpenMP implementations (A100) | . 206 |

# LIST OF TABLES

| Tab | Page                                                                    |

|-----|-------------------------------------------------------------------------|

| 1.  | Summary of heterogeneous computing challenges addressed in each chapter |

| 2.  | Comparison of CUDA and OpenCL GPGPU abstractions                        |

| 3.  | OpenACC and OpenCL benchmarks evaluated using FPGAs 84                  |

| 4.  | Intel and Xilinx Hardware Resource Features                             |

| 5.  | FPGA-specific collapse clause performance comparison (Stratix V)        |

| 6.  | SRAD FPGA reduction performance comparison (Stratix V)                  |

| 7.  | HotSpot code motion performance evaluation (Stratix V)                  |

| 8.  | SRAD benchmark resource usage data (Arria 10)                           |

| 9.  | SRAD benchmark resource usage data (Stratix 10)                         |

| 10. | Jacobi benchmark resource usage data (Arria 10)                         |

| 11. | Jacobi benchmark resource usage data (Stratix 10)                       |

| 12. | LULESH benchmark resource usage data (Stratix 10)                       |

| 13. | List of kernels ported from Intel OpenCL to Xilinx OpenCL               |

| 14. | Examples of straightforward directive translations implemented in CCAMP |

| 15. | SPEC Accel Benchmark Attributes                                         |

| 16. | Naive Jacobi and Matmul OpenMP 4+ Run Times Optimized with CCAMP        |

| 17. | Exascale Programming Models and Implementations Explored 188            |

| 18. | Runtime performance comparison of Level0 and OpenCL backends 205        |

# LIST OF SOURCE CODE LISTINGS

| Listing |                                                                   | F | <b>e</b> age |

|---------|-------------------------------------------------------------------|---|--------------|

| 1.1.    | Example CUDA C Application                                        |   | 19           |

| 1.2.    |                                                                   |   | 49           |

| 1.3.    |                                                                   |   | 50           |

| 1.4.    |                                                                   |   | 50           |

| 2.1.    | Code Motion: Input conditional                                    |   | 64           |

| 2.2.    | Code Motion: Modified conditional                                 |   | 64           |

| 2.3.    | Code Motion: After code motion                                    |   | 64           |

| 2.4.    | OpenACC Single work-item directives                               |   | 67           |

| 2.5.    | OpenACC nested loops with collapse clause                         |   | 68           |

| 2.6.    | OpenACC loop after collapse transformation                        |   | 68           |

| 2.7.    | OpenACC sum reduction                                             |   | 71           |

| 2.8.    | OpenCL generated from OpenARC's FPGA-specific                     |   |              |

|         | reduction transformation                                          |   | 73           |

| 2.9.    | OpenACC with window directive                                     |   | 78           |

| 2.10    | . Transformed OpenCL sliding window code                          | • | 81           |

| 2.11    | . Transformed OpenCL sliding window code with loop unrolling      |   | 83           |

| 2.12    | . Inferring a shift register using the Intel and Xilinx platforms |   | 129          |

| 3.1.    | Naive OpenMP Jacobi CCAMP Optimization                            |   | 157          |

| 3.2.    | Naive OpenACC Matmul Optimization                                 |   | 158          |

### CHAPTER I

### INTRODUCTION, BACKGROUND, AND MOTIVATION

Heterogeneous computing has undoubtedly become a permanent resident in the high-performance computing (HPC) landscape. The idea of using a diversity of hardware devices or systems together to solve a single problem is already a reality in today's leading supercomputer systems [1, 2]. The upcoming exascale systems, the largest and most powerful computing machines ever built, all depend innately on heterogeneous design [3, 4, 5]. As we approach the physical limitations of CPU-based fabrics, advancement in computational system design will require specialization not just in terms of processors and accelerators, but also memory hierarchies, storage, and more. While this era of extreme heterogeneity [6] will certainly give rise to interesting and powerful machines, it will also give rise to significant challenges. Below, we lay out the most significant and universal challenges in today's and tomorrow's heterogeneous programming and computing landscape, and describe how this dissertation's contributions move us one step closer to a solution.

A - Diversity of Hardware: In this dissertation, we discuss projects involving both GPU and FPGA accelerators. However, for upcoming and future systems, other types of accelerators besides GPUs and FPGAs are being explored as hardware accelerators. More exotic, customized, and specialized hardware accelerators are being explored as viable options in heterogeneous systems. Machine learning accelerators, neuromorphic chips, and quantum accelerators promise to bring incredible performance to science, but also incredible challenges. As we see in this dissertation, the introduction of GPU and FPGA accelerators has already created hurdles for efficient heterogeneous computing.

- B Diversity of Programming Models: The diversity of heterogeneous hardware has already led to a diversity of high-performance programming models. This will undoubtedly be exacerbated as we transition toward extreme heterogeneity. While this diversity of models may appear necessary to support the wide range of devices, it leaves classes of devices inaccessible to classes of application developers.

- C Abstraction Level for Scientific Computing: Another point of contention in contemporary heterogeneous programming is the appropriate abstraction level for programming models. While computer scientists and professional programmers may prefer lower-level models that provide opportunities to fine-tune applications to specific devices, domain scientists may prefer a higher-level model that allows for portability between ecosystems. This can again lead to divergent programming models. DSLs like Tensorflow [7] may provide an optimal high-level approach, and these DSLs can be built using generalized low-level approaches. However, this has stranded the programmer looking for a high-level heterogeneous programming approach for an application outside the popular DSL frameworks.

- D Balance Between Open-Source and Proprietary: Another significant trade-off is the balance between open-source and proprietary frameworks. Nvidia's CUDA Toolkit [8] has been extremely successful as a frontier of GPU-CPU heterogeneous computing. Because of the toolkit's proprietary nature, Nvidia has been financially motivated to maintain, update, document, and market its tools, which has led to widespread adoption and longevity. However, the successes of a proprietary framework are less likely to extend to an extremely heterogeneous environment. An alternative could be open source solutions and

Table 1. Summary of heterogeneous computing challenges addressed in each chapter.

A - Diversity of Hardware,

B - Diversity of Programming Models,

C - Abstraction Level for Scientific Computing,

D - Balance Between Open-Source and Proprietary

| Chapter I   | Introduction |

|-------------|--------------|

| Chapter II  | A, C         |

| Chapter III | A, B         |

| Chapter IV  | A, B, C, D   |

| Chapter V   | Conclusion   |

standards like OpenMP, but these solutions may experience less streamlined development. For example, the OpenMP offloading standard was first released in 2013, but the first fully functional implementations were very recently released.

Working Toward Solutions - This Dissertation: In this dissertation, we push directive-based programming forward as one solution to the challenges above. In Table 1, we list the specific challenges addressed in each chapter of this dissertation. Our main research question is as follows: Can an open-source, high-level, directive-based programming approach deliver specialized performance on the diversity of contemporary heterogeneous accelerators and exascale hardware?

This question is directly related to each of the challenges mentioned above. (A) Because of its high-level nature, a directive-based solution can more easily incorporate new heterogeneous device families without significant restructuring of a language or standard. In contrast, a lower-level approach may need to be significantly extended or specialized to support a new device. (B) A single directive-based approach with implementations across systems can circumvent the issue of branching programming models designed for specific devices. (C) The

abstraction level of directive-based models can be more palatable for scientists from different domains compared to lower-level languages. And finally, (D) an open-source directive-based standard allows for wide adoption across ecosystems, even if implementations on specific platforms internally rely on proprietary backends.

We now present an outline of this dissertation. In Chapter I, we introduce the history of heterogeneous computing, and the contemporary programming models and compiler frameworks most commonly featured in heterogeneous computing-related research and science. We also discuss the available benchmark suites designed to evaluate heterogeneous platforms. The material in this chapter is unpublished with no co-authorship, although revision suggestions were given by Seyong Lee and the dissertation committee (Allen Malony, Hank Childs, Boyana Norris) as part of an Area Exam submission.

In Chapter II, we address the diversity of hardware by presenting an OpenACC-to-FGPA framework that encapsulates FPGAs under the umbrella of directive-based acceleration. Using this framework, a single application written using OpenACC can be run on a CPU, GPU, and FPGA. Within the framework, device-specific compiler optimizations produce low-level code specific to the targeted hardware. This framework is also one solution to the abstraction level for scientific computing, as it provides a palatable programming abstraction level for a very specialized device. Chapter II contains previously published material with co-authors from ICS 2018 [9], AsHES 2020 [10], PARCO 2021 [11], and IWOCL 2021 [12].

In Chapter III, we introduce an OpenACC and OpenMP interoperable framework that addresses the *diversity of programming models* between the two most widely used directive-based standards. This framework also addresses the

diversity of hardware by allowing a single application written in one standard to execute on any device supporting either standard. Chapter III contains previously published material with co-authors from HeteroPar 2019 [13] and SC 2020 [14].

In Chapter IV we present an exploration of exascale-intended platforms using applications written in a single programming model, OpenACC. Each OpenACC application is then source-to-source translated and compiled to several different platforms. This addresses all four problems above: (A and B - diversity of hardware and programming models) we target multiple different hardware accelerators using not only a single programming model, but a single source code without modification, (C - abstraction level for scientific computing) we assess a single high-level directive-based abstraction model for several specialized platforms, and (D - balance between open-source and proprietary) our evaluated applications are written using a single open-source standard, and source-to-source translated using an open-source compiler into several proprietary low-level programming models, allowing us to take advantage of both ownership approaches. Chapter IV contains unpublished material with co-authors.

Finally, in Chapter V we make a high-level assessment of contemporary heterogeneous computing, summarize the research in this dissertation, and discuss avenues for future research. Chapter IV contains unpublished material.

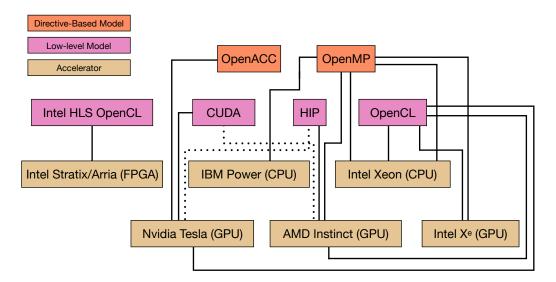

In Figure 1, we see a summary, albeit simplified, of the current state of heterogeneous computing. We see directive-based programming models, low-level models, and accelerators. The solid lines here means a mainstream implementation supports compilation of a model on an accelerator or device, while a dotted line indicates supports with extra steps. While there is some overlap between models on many platforms, even in these cases, the code written in the same standard

Figure 1. Summary of the state of heterogeneous programming and computing.

may not be directly portable between the platforms. Furthermore, for devices with support for multiple programming models, the associated implementations may be significantly more mature for a single model or subset of the technically supported models. Figure 1 succinctly exposes the challenges mentioned above.

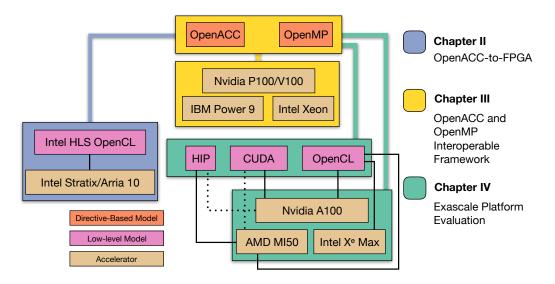

Figure 2. Re-evaluation of the state heterogeneous programming and computing after including this dissertation's contributions.

In Figure 2, we see a re-imagined landscape for heterogeneous computing as a result of the research in this dissertation. Because of the contributions in Chapter III, we can now encapsulate OpenACC and OpenMP as an interchangeable, high-level, front-end programming model. The contributions of Chapter II allow us to include Intel FPGAs into this encapsulation, instead of relying on Intel-specific OpenCL. Finally, due to the contributions of Chapter IV, we see the diversity of low-level models and devices that can be evaluated using a single directive-based frontend and a sufficiently optimized source-to-source compiler. Throughout the rest of this dissertation, we take an extended dive into these three projects, and examine how the performed research motivates Figure 2.

This dissertation includes prose, figures, and tables from previously published conference, workshop, and journal proceedings.

### 1.1 History of Heterogeneous Computing

Heterogeneous computing is paramount to today's high-performance systems. The top and next generation of supercomputers all employ heterogeneity, and even desktop workstations can be configured to utilize heterogeneous execution. The explosion of activity and interest in heterogeneous computing, as well as the exploration and development of heterogeneous programming approaches, may seem like a recent trend. However, heterogeneous programming has been a topic of research and discussion for nearly four decades. Many of the issues faced by contemporary heterogeneous programming approach designers have long histories, and have many connections with now antiquated projects, ideas, and technologies.

In this section, we explore the evolution and history of heterogeneous computing, with a focus on the development of heterogeneous programming approaches. In Section 1.1.1, we do a deep dive into the field of distributed heterogeneous programming, the first major application of hardware heterogeneity in computing. We also briefly explore the phasing-out of distributed heterogeneous systems and approaches, and discuss the transitional period for the field of heterogeneous computing. In Section 1.1.2, we provide an exploration into contemporary accelerator-based heterogeneous computing, specifically analyzing the different programming approaches developed and employed across different accelerator architectures.

1.1.1 Distributed Heterogeneous Systems. Even 40 years ago, computer scientists realized heterogeneity was needed due to diminishing returns in the homogeneous systems. In the literature, the first references to the term "heterogeneous computing" referenced the distinction between single instruction, multiple data (SIMD) and multiple instruction, multiple data (MIMD) machines in a distributed computing environment.

Several machines dating back to the 1980s were created and advertised as heterogeneous computers. Although these machines were conceptually different than today's heterogeneous machines, they still were created to address the same challenges: using optimized hardware to execute specific algorithmic patterns.

The Partitionable SIMD/MIMD (PASM) [15] machine developed at Purdue University in 1981 was initially developed for image processing and pattern recognition applications. PASM was unique in that it could be dynamically reconfigured into either a SIMD or MIMD machine, or a combination thereof. The goal was to create a machine that could be optimized for different image processing and pattern recognition tasks, configuring either more SIMD or MIMD capabilities depending on the requirements of the application.

However, like many early heterogeneous computing systems, programmability was not the primary concern. The programming environment for PASM required the design of a new procedure-based structured language similar to TRANQUIL [16], the development of a custom compiler, and even the development of a custom operating system.

Another early heterogeneous system was TRAC, the Texas Reconfigurable Array Computer [17], built in 1980. Like PASM, TRAC could weave between SIMD and MIMD execution modes. But also like PASM, programmability was not a primary or common concern with the TRAC machine, as it relied on now-arcane Job Control Languages and APL source code [18].

The lack of focus on programming approaches for early heterogeneous systems is evident in some ways by the difficulty in finding information on how the machines were typically programmed. However, as the availability of heterogeneous computing environments increased throughout the 1990s, so did the research and development of programming environments.

Although the first heterogeneous machines consisted of mixed-mode machines like PASM and TRAC, mixed-machine heterogeneous systems became the more popular and accessible option throughout the 1990s. Instead of a single machine with the ability to switch between a synchronous SIMD mode and an asynchronous MIMD mode, mixed-machine systems contained a variety of different processing machines connected by a high-speed interconnect. Throughout the 80s and early 90s, this environment expanded to include vector processors, scalar processors, graphics machines, etc.

Examples of machines used in mixed-machine systems include graphics and rendering-specific machines like the Pixel Planes 5, Silicon Graphics 340 VGX,

SIMD and vector machines like the MasPar MP-series and the CM 200/2000, and coarse-grained MIMD machines like the CM-5, Vista, and Sequent machines.

It was well understood that different classes of machines (SIMD, MIMD, vector, graphics, sequential) excelled at different tasks (parallel computation, statistical analysis, rendering, display), and that these machines could be networked together in a single system. However, coordinating these distributed systems to execute a single application presented significant challenges.

The 1988 work by Ercegovac [19], Heterogeneity in Supercomputer

Architectures, represents one of the first published works specifically surveying the

state of high performance heterogeneous computing. They define heterogeneity as

the combination of different architectures and system design styles into one system

or machine, and their motivation for heterogeneous systems is summed up well by

the following direct quote:

Heterogeneity in the design (of supercomputers) needs to be considered when a point of diminishing returns in a homogeneous architecture is reached.

As we see throughout this work, this drive for specialization to counter diminishing returns from existing hardware repeatedly resurfaces, and this motivation for heterogeneous systems is very much relevant today.

At the time of Ercegovac's work, there existed three primary homogeneous processing approaches in high-performance computing: (1) vector pipeline and array processors, (2) multiprocessors and multi-computers following the MIMD model, and (3) attached SIMD processors. These approaches were ubiquitous across all the early surveyed works related to distributed heterogeneous computing,

and they heavily influenced the construction of heterogeneous systems and the development of heterogeneous software and programming approaches.

A later survey was published in 1995: Goals of and Open Problems in High-Performance Heterogeneous Computing by Siegel et al. [20]. Siegel was very involved in the early development of distributed heterogeneous computing, including the outline of the PASM system mentioned above. The authors presented the following goal for heterogeneous computing:

To support computationally intensive applications with diverse computing requirements. Ideally presented to the user in an invisible way.

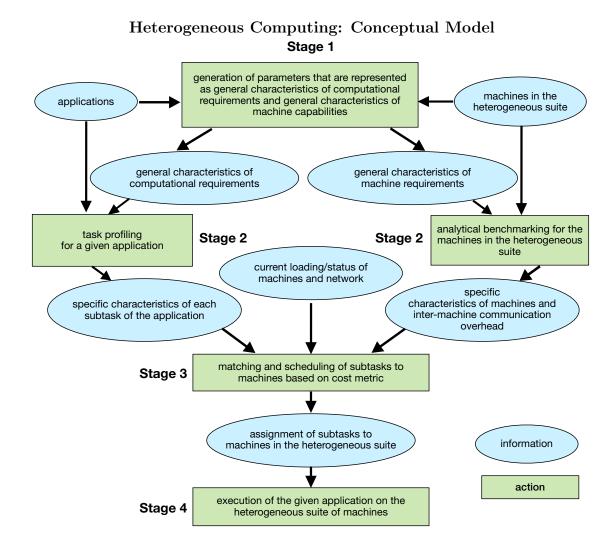

Looking to the future, this survey by Siegel et al. introduced a conceptual model for an end-to-end heterogeneous programming and computing approach, recreated for this dissertation in Figure 3. Although the model is conceptual, as no complete implementation existed at the time, the model and derivations of it appear frequently in the subsequent heterogeneous computing literature. The concepts of 1) automated machine and algorithm classification, 2) automated task profiling and analytical benchmarking, and 3) automated scheduling and assignment of sub-tasks to heterogeneous components were open questions at the time, and largely remain open questions today.

While most parallel computing research at the time focused on computational models, algorithms, or machine architectures, the PVM project [21], started at Oak Ridge National Laboratory, was an early attempt to provide a unified programming model for both homogeneous and heterogeneous distributed environments. The overarching goal of PVM was to allow a diverse and scalable set of heterogeneous computer systems to be programmed as a single parallel

Figure 3. Re-creation of conceptual model of heterogeneous computing by Siegel et al. [20]

virtual machine. Essentially, PVM was designed as a programming environment for interacting but independent components. Other early heterogeneous programming languages included HeNCE [22, 23, 24], an extension to PVM, the p4 project [25] from Argonne National Laboratory, and the Mentat Language [26, 27], developed as extensions to C++.

Thirty years later, many of the visions of the developers of early distributed heterogeneous systems are still just that—visions. As we see in the later chapters and sections of this dissertation, most modern heterogeneous programming approaches still require some manual management of data transfers, communication, and synchronization, although typically with more user-friendly programming approaches than those of early systems like Mentat. Much of the research and discussion today in heterogeneous computing revolves around finding the appropriate abstraction level, as previously mentioned.

The diversity of processors in these early heterogeneous distributed systems seems small relative to today's array of co-processors (GPUs, FPGAs, TPUs, etc.). These early processors would all typically fall into the "traditional CPU" in today's categorization.

However, the diversity in supporting hardware and software was far greater in early heterogeneous ecosystems than today's typical cluster and supercomputer environments. Because the sub-components were typically completely separate machines, they experienced heterogeneity in the network architecture, the connection latencies, and the different communication bandwidths for different machines. On the software side, different machines had different operating systems, different process support and inter-process communications, varied compiler and language support, and multiple file systems. Unlike today's cluster and

supercomputing environments with mostly homogeneous software environments, early distributed heterogeneous system approaches required masking these network and software diversities. However, as we transition into an era of extreme heterogeneity, many of these early considerations are likely to resurface.

Around the turn of the century, the keywords and terminology surrounding heterogeneous distributed systems research began to shift. The next realization of heterogeneous computing systems began to be referred to as Metasystems, or referenced in the context of Metacomputing, and Grid Computing. This shift in perspective reflected a more universal or global outlook on heterogeneous computing. Distributed heterogeneous computing, coincident with the rapid and impressive growth of the internet and web-based computing, expanded into Metacomputing, Grid Computing, and eventually set up the backbone for the monolith that is today's cloud-based computing.

The goals of Meta and Grid computing were to create infinitely scaling systems by harnessing the power of remotely connected heterogeneous systems. While some projects tackled this, these ideas were ultimately re-purposed for commercial success under the umbrella of cloud computing. Additionally, with respect to scientific endeavors, the construction of large-scale homogeneous clusters and supercomputers beckened a shift from distributed heterogeneous machines. At the same time, the growth of MPI, without a major focus on heterogeneous interoperability, overshadowed projects like PVM and p4 that targeted heterogeneous systems.

Finally, the very things that made early machines heterogeneous began to be integrated into single homogeneous processors. Unlike mixed-mode machines like PASM with distinct SIMD and MIMD processing, many new multi-core vectorizing processors seamlessly integrate both SIMD and MIMD capabilities, which forgoes the need for a heterogeneous programming environment. Similarly, as we previously discussed, early distributed heterogeneous systems contained separate processors for visualization, statistics, and data processing. However, with the expansion of x86 and inclusion of specialized and vector instructions on general purpose CPU processors, the problems these early heterogeneous systems tackled could now be solved by homogeneous systems.

The shift into cloud computing, the ubiquity of MPI, and the continuous consolidation into x86 CPUs in many ways signaled the end of heterogeneous computing as it was originally imagined. However, as we see in the next section (Section 1.1.2), the rebirth of heterogeneous computing, and reinvention of many of the ideas previously mentioned, was sparked by the introduction of accelerator-based heterogeneous systems.

#### 1.1.2 Multicore, Manycore, and Accelerator-based

Heterogeneous Systems. Hardware processing chips evolved from a single core, to multi-core and manycore chips, which then developed into hardware accelerators. These developments revolutionized the architectures of nearly all high-performance machines, and effectively re-birthed the field of heterogeneous computing.

The construction of large homogeneous machines marked the end of the 2000s decade and the end of heterogeneous distributed systems like we saw in the 1980s and 1990s. Jaguar [28], built around 2009 at Oak Ridge National Laboratory, was a Cray XT5 system, consisting of 224,256 x86-based AMD CPU cores, and was listed as the world's fastest machine in 2009 and 2010. Kraken [29], another Cray Xt5 system built in 2009, was listed as the world's fastest academic machine at the time. These homogeneous machines dominated the domain of HPC for

several years. Likewise, HPC software support, programming approaches, and compiler infrastructure developed during this time was also largely homogeneous. However, at the same time, scientific programmers began experimenting with programming using Graphics Processing Units, or GPUs, a trend that would eventually revolutionize the HPC field.

In 2000, Toshiba, Sony, and IBM collaborated on the Cell Project [30]. This project culminated in the release of the Cell Processor in 2006. While not strictly a GPU, the Cell Processor was one of the first architectures to apply accelerator-based heterogeneity to multi-media and general purpose applications. The Cell Processor's first major commercial application was inside the Sony PlayStation 3 gaming console. In 2008, IBM and Los Alamos National Laboratory (LANL) released the Roadrunner supercomputer, which consisted of a hybrid design with 12,960 IBM PowerXCell and 6,480 AMD Opteron dual-core processors [31]. The IBM PowerXCell processors absorbed the original Cell processor design.

While the Cell processor generated excitement and a new interest in a different type of heterogeneous computing, it was only efficient for certain computations, and the overhead of manually transferring memory to and from the device was a performance bottleneck due to the small memory size of the Cell architecture. Although GPUs and other heterogeneous accelerators suffer from these same issues, they evolved and developed to meet the demand of scientific computing.

The scientific community began evaluating GPUs for general purpose processing well before their use became mainstream. In 2001, researchers evaluated general purpose matrix multiplication, and in 2005 LU decomposition on a GPU was shown to outperform a CPU implementation [32]. Interest in utilizing GPUs

in scientific computing continued to grow, but was inhibited by the complex programming approaches for GPUs, which typically required a low-level graphics interface and dealing with shaders and graphics-related APIs data structures. However, with the release and development of programming models and frameworks mentioned in subsequent sections, GPU programming, and the whole field of scientific heterogeneous programming including other types of accelerators, became the norm in high-performance computing. Throughout the rest of this dissertation, references to "heterogeneous computing" typically imply the contemporary accelerator-based flavor.

Since the initial release of CUDA in 2006, GPGPUs have been the dominant driving force for accelerator-based heterogeneous computing. The concept of offloading computationally intense regions of code to a heterogeneous hardware accelerator has become commonplace in scientific computing, and for the past decade, heterogeneous computing has almost exclusively referred to GPGPU offloading. However, FPGAs have recently emerged as a potential competitor to GPU accelerators, both in terms of computing power and power efficiency.

Field Programmable Gate Arrays (FPGAs) have been designed and developed for nearly 40 years. Altera, a major FPGA manufacturer, was founded in 1983, and released the first FPGA in 1984. Xilinx, the main competitor to Altera for several decades, was founded in 1984 and released their first FPGA in 1985. These devices have been promoted as potential architectures for high performance computing for decades, but until very recently, have not seen much adoption. The real revolution for FPGAs, and their adoption as a heterogeneous accelerator, has stemmed from the introduction of new FPGA programming approaches. Creating

a high-level programming approach for high-performance FPGA accelerators is the main motivation for Chapter II.

### 1.2 Heterogeneous Programming Models

In this section, we first discuss the accelerator-based heterogeneous programming models most heavily featured in this dissertation's research results. We then discuss several other relevant contemporary heterogeneous programming models.

1.2.1 CUDA. Nvidia was formed in 1993, but first gained major recognition by winning the contract to develop the graphics hardware for the Microsoft Xbox gaming console in 2000. Nvidia continued to grow and increase its claim in the GPU market with the release of the GeForce line, in direct competition with AMD's Radeon line. However, these devices were still targeted toward graphics processing.

As the interest in scientific computing using GPUs continued to grow, Nvidia first recognized the potential financial advantages of supporting this community. In 2007, Nvidia launched the Tesla GPU, aimed at supporting general purpose computing, and the CUDA (Compute Unified Device Architecture) API and programming platform [8].

The CUDA programming platform abstracted programming GPU hardware into an API that was more consumable by scientific programmers and other programmers without extensive graphics programming experience. The CUDA programming model essentially presents a hierarchical multi-threading layout, where threads are executed as a 32- or 64-thread warp, warps are mapped onto thread-blocks, and thread-blocks are mapped onto a grid and grid blocks. These abstractions fit quite naturally with the nested loop structure of most scientific

Listing 1.1 Example CUDA C Application

```

#include <stdio.h>

2

void saxpy(int n, float a, float *x, float *y)

4

5

int i = blockIdx.x*blockDim.x + threadIdx.x;

6

7

if (i < n) y[i] = a*x[i] + y[i];

q

10

int main(void)

11

12

int N = 1 << 20;

13

float *x, *y, *d_x, *d_y;

14

x = (float*)malloc(N*sizeof(float));

15

y = (float*)malloc(N*sizeof(float));

16

cudaMalloc(&d_x, N*sizeof(float));

17

18

cudaMalloc(&d_y, N*sizeof(float));

19

20

for (int i = 0; i < N; i++) {

x[i] = 1.0f;

21

y[i] = 2.0f;

22

23

24

25

cudaMemcpy(d_x, x, N*sizeof(float), cudaMemcpyHostToDevice);

26

cudaMemcpy(d\_y,\ y,\ N*sizeof(float),\ cudaMemcpyHostToDevice);

27

28

// Perform SAXPY on 1M elements

29

saxpy <<<(N+255)/256, 256>>>(N, 2.0f, d_x, d_y);

30

31

cudaMemcpy(y, d_y, N*sizeof(float), cudaMemcpyDeviceToHost);

32

33

cudaFree(d_x);

34

cudaFree(d_y);

35

free(x);

36

free(y);

37

```

software. Listing 1.1 shows an example CUDA application, sourced from Nvidia's website [33].

As the popularity of CUDA and GPGPU programming grew, several large supercomputers began including both host CPUs and GPU accelerators. In 2010, China's Tianhe-1A machine launched, containing 14,336 Xeon X5670 processors and 7,168 Nvidia Tesla M2050 general purpose GPUs [34]. This heterogeneous machine overtook the previously mentioned Jaguar machine from Oak Ridge National Laboratory (ORNL) as the "world's fastest supercomputer". ORNL's Titan supercomputer, a successor Jaguar, launched in 2013 and consisted of 18,688

AMD Opteron CPUs, each with an attached Nvidia Tesla (K20x) GPU [35]. This machine also secured the top spot as the world's fastest machine.

More recently, Nvidia GPUs and CUDA programming were employed in ORNL's Summit Supercomputer [1], another machine that briefly held the title as the world's fastest. Summit was launched in 2018 and contains 4,608 nodes each with 6 Nvidia Tesla V100 GPUs. Similarly, Lawrence Livermore National Laboratory (LLNL) launched the Sierra Supercomputer [2] in 2018, containing 4,320 nodes each with 4 Nvidia Tesla V100 GPUs.

Much of CUDA's success in scientific programming can be attributed to Nvidia's continued investment in and focus on CUDA training. Online and inperson training workshops, and a surplus of available training materials, made Nvidia and CUDA an attractive GPGPU option compared to other vendors. This focus on training and CUDA's success should provide a model for future heterogeneous programming approaches. Some newer approaches like OpenACC (also supported by Nvidia, and discussed in detail in Section 1.2.4) have also adopted this strategy, frequently hosting learning-focused hackathons and generating significant training materials [36].

In this dissertation, CUDA is employed as a backend programming model in Chapter IV.

1.2.2 OpenCL. CUDA's dependence on Nvidia devices spawned efforts to create an open-source alternative. OpenCL was developed as one alternative[37]. As we see in the remainder of this dissertation, OpenCL has become a staple of accelerator-based heterogeneous programming approaches, both as a stand-alone approach and as an intermediate representation or backend for higher-level approaches.

OpenCL (Open Computing Language) was originally developed by Apple as a GPGPU option under the OSX umbrella. In early 2008, Apple submitted a proposal to the Khronos Group for creation and management of an OpenCL standard [37]. On November 18, 2008 the OpenCL 1.0 technical specification was released. By the end of 2008, AMD, Nvidia, and IBM had all incorporated OpenCL support into their vendor toolchains.

Like CUDA, the OpenCL programming approach separates an application into host code and device code. The abstraction level for the OpenCL device code is very similar to CUDA, but the host code abstractions are arguably more verbose. Like CUDA, GPU cores are abstracted into a tiered parallelism. In OpenCL, work-items are executed as part of a work-group, and work-groups are organized inside an ND range (Table 2). Listing 1.2 demonstrates and example vector addition application in OpenCL. From the line count alone, we can see that OpenCL requires a significant amount of low-level and boilerplate code, although this functionality is typically encapsulated in routines and libraries by frequent OpenCL programmers. However, each programmer creating a personalized set of routines to abstract OpenCL API calls creates issues with code portability and interpretability.

Although OpenCL does provide an open-source alternative to CUDA that is supported across several different device vendors (Nvidia, Intel, IBM, AMD), it has not become the de facto standard for heterogeneous GPGPU computing. First, the widespread success of CUDA and Nvidia's dominance in the GPGPU market has allowed scientific programmers to safely choose a non-portable option. Second, the abstraction level, especially the verbosity of the host code, has led many GPGPU developers to seek higher-level abstractions, as we see in the following section.

Table 2. Comparison of CUDA and OpenCL GPGPU abstractions

| CUDA         | OpenCL     |

|--------------|------------|

| Grid         | NDRange    |

| Thread Block | Work group |

| Thread       | Work item  |

| Thread ID    | Global ID  |

| Block index  | Block ID   |

| Thread index | Local ID   |

However, as we discuss later, although OpenCL has not seen widespread adoption as a programming approach, many frameworks and compilers target OpenCL as a backend API (OneAPI [38], OpenARC [39], TVM [40], etc.)

The OpenCL programming model is a critical component of this dissertation, and is featured as a backend programming target in Chapters II and IV.

1.2.3 HIP. Nvidia's main competitor in the GPU market, traditionally in the consumer market but more recently also in the high-performance and scientific community, is AMD. Unlike Nvidia, AMD has not developed a proprietary programming approach and vendor compiler for heterogeneous computing. Instead, to support its GPU architectures AMD has developed the open-source ROCm (Radeon Open Compute) suite [41]. ROCm is a collection of APIs, drivers, and development tools that support heterogeneous execution on both AMD GPUs, but also other architectures like Nvidia GPUs. The actual programming model developed as part of ROCm is HIP, another low-level approach with a similar abstraction level to CUDA and OpenCL. However, the ROCm toolkit and associated compilers also support OpenMP and OpenCL applications. The compilers, libraries, and debuggers for ROCm are available from the open-source github [42]. Although the current generation of top

supercomputers like Sierra and Summit employ Nvidia GPUs, future systems like ORNL's Frontier [3], expected to launch in 2021, will employ AMD GPUs. This transition could herald a shift away from CUDA, and increase the use of ROCm and HIP across all of scientific computing.

In this dissertation, HIP is employed as a backend programming model in Chapter IV.

1.2.4 OpenACC. OpenACC (originally short for Open Accelerators) is one of this first high-level (as opposed to low-level approaches like HIP, OpenCL, and CUDA) GPGPU programming approaches that still supports a significant user base today (as of 2021). OpenACC was first released in 2012 as a collaboration between Cray, NVIDIA, and the Portland Group in order to support the users of ORNL's Titan, one of the first large heterogeneous supercomputers. As previously mentioned, Titan was a Cray machine with Nvidia devices. The Portland Group was involved because OpenACC was inspired by the high-level directive approach used in in the PGI-Accelerator model, and the first OpenACC compiler provided by PGI was developed as an extension to the PGI-Accelerator compiler [43, 44].

The dream of OpenACC was to create an open, directive-based standard for GPU-computing as an analog and counterpart to the then de facto standard for parallel processing on multi-core CPUs, OpenMP. In the same way that a small number of OpenMP pragmas can be used to parallelize an existing application, OpenACC intended to provide a minimal set of directives that application developers could apply to accelerate an existing CPU-based scientific application on a GPU. This contrasted with the existing lower-level programming approaches like CUDA and OpenCL, which required a significant amount of code restructuring and rewriting for GPU acceleration.

The ideology of OpenACC is to allow users to expose and identify parallelism in an application using descriptive directives, and to leave the more complicated task of mapping parallelism to GPU devices in the hands of the OpenACC compiler. This deviates from the OpenMP model, which traditionally employed a very moderated and prescriptive application of directives.

This high burden of effort tasked to OpenACC compilers in some ways has prevented OpenACC from reaching the popularity and monopoly status of its OpenMP analog. Although OpenACC is intended for general-purpose GPU computing across different vendors, for most of its history, the PGI OpenACC compiler has been the only available production-level option, and was restricted to Nvidia devices. Now, nearly a decade later, other implementations have more fully adopted the OpenACC standard and implemented more functional support. We discuss these compilers in more detail in Section 1.3.

An OpenACC annotated application typically contains a combination of data and compute directives centered around a computationally intense region of code or loop nest. In Listing 1.3, we see a small C program annotated with two OpenACC directives, a data directive (line 16) and a compute directive (line 19). Replicating this high-level programming approach in a low-level approach like CUDA or OpenCL would require significantly more code, several source files, and multiple compilations.

OpenACC is featured heavily in this dissertation's research results, most often as the primary source code language for evaluations in Chapters II, III, and IV.

1.2.5 OpenMP. OpenMP reigned as the de facto standard for directive-based homogeneous multi-core CPU computing throughout the early

2000s, at least in the scientific computing domain. As the demand for high-level programming approaches for GPGPU computing increased in the early 2010s, there was a push for OpenMP to support accelerator-based heterogeneous computing in addition to the homogeneous multi-core computing. Although the previously-mentioned OpenACC was developed to address this demand, motivation for OpenMP prevailed for several reasons:

- OpenACC and OpenACC compilers have been too-tightly bundled to Nvidia devices, especially since PGI (the primary OpenACC compiler) was acquired by Nvidia in 2013.

- 2. Most high-performance-oriented scientific programmers were already familiar with basic OpenMP directives and OpenMP programming styles.

- Many scientific applications already employed OpenMP for homogeneous CPU-based computing, lightening the burden of developing a new acceleratorbased implementation.

As a result, in 2013, a year after the launch of OpenACC, the OpenMP standards committee released OpenMP 4.0, which included new directives for offloading to GPU accelerators. In 2018, the standards committee released OpenMP 5.0, which expanded support for accelerators and included additional directives for tasking and auto-parallelism. Even before the official inclusion of offloading directives in OpenMP, several research-oriented compilers had been prototyping support for GPU offloading for OpenMP [45, 46].

Initially in their development, OpenACC and OpenMP differed in their programming approach philosophy. As mentioned, OpenACC employed a more descriptive approach, where users expose parallelism and compilers map that

parallelism to devices. In OpenMP, the directives supplied by users are taken more literally and prescriptively, in that the user directly controls how the parallelism is mapped to a device. However, the two standards have recently become more aligned due to the *loop* directive introduced in OpenMP 5.0, which mimics the behavior of the descriptive OpenACC directives. The relationship between OpenMP and OpenACC has been somewhat contentious at times. However, both standards are still currently being maintained as a high-level programming approach for heterogeneous computing.

Although OpenACC has been limited due to its ties to Nvidia devices, the availability of the production-level PGI OpenACC compiler throughout its history has certainly been an advantage. In contrast, although OpenMP 4.0 originally was approved in 2013, compilers fully supporting the standard have been slow in coming. Only very recently have mature compilers successfully supported the entire standard, and many mainstream compilers are still under development for the OpenMP 4.0 standard and especially the OpenMP 5.0 updates. We discuss this further in Section 1.3.

In Listing 1.4, we show the same application as the previous listing, now annotated with OpenMP directives. Although this short example trivially highlights the use of OpenMP, the example still demonstrates how OpenMP greatly simplifies heterogeneous computing compared to CUDA and OpenCL.

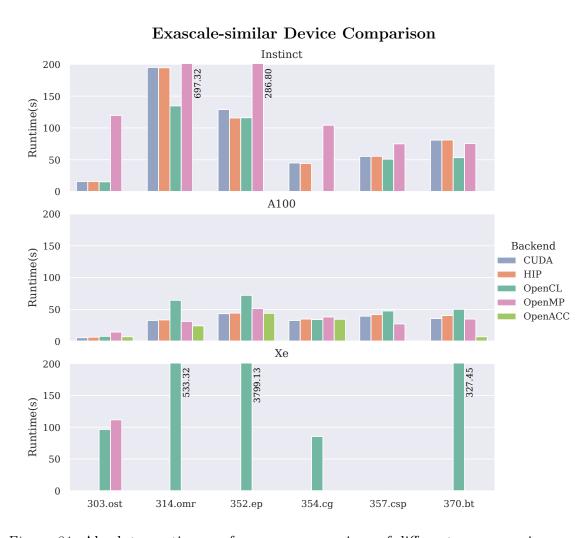

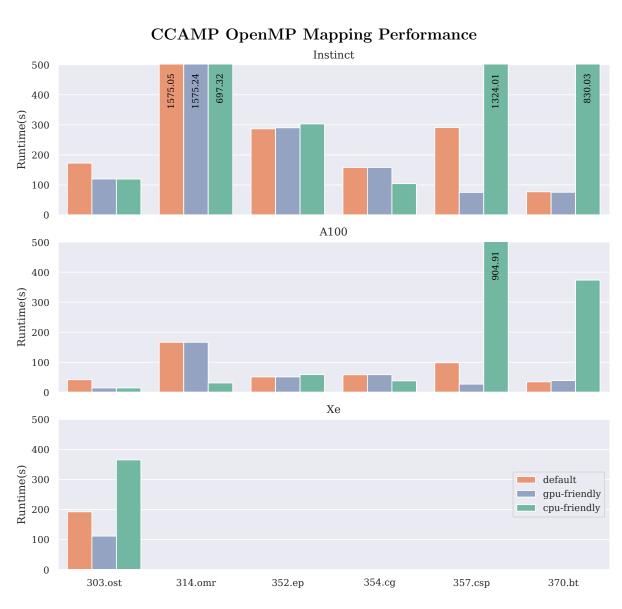

1.2.6 Other Modern Programming Models. Although the previous sections describe the programming models targeted in the research results of this dissertation, for the sake of completeness we briefly describe several other contemporary heterogeneous programming models.