# ACCELERATING MACHINE LEARNING VIA MULTI-OBJECTIVE OPTIMIZATION

by

# ROBERT LIM

# A DISSERTATION

Presented to the Department of Computer and Information Science and the Division of Graduate Studies of the University of Oregon in partial fulfillment of the requirements for the degree of Doctor of Philosophy

September 2021

## DISSERTATION APPROVAL PAGE

Student: Robert Lim

Title: Accelerating Machine Learning via Multi-Objective Optimization

This dissertation has been accepted and approved in partial fulfillment of the requirements for the Doctor of Philosophy degree in the Department of Computer and Information Science by:

Allen Malony Chair

Boyana Norris Core Member Dejing Dou Core Member Camille Coti Core Member

William Cresko Institutional Representative

and

Andy Karduna Interim Vice Provost for Graduate Studies

Original approval signatures are on file with the University of Oregon Division of Graduate Studies.

Degree awarded September 2021

© 2021 Robert Lim All rights reserved.

## DISSERTATION ABSTRACT

Robert Lim

Doctor of Philosophy

Department of Computer and Information Science

September 2021

Title: Accelerating Machine Learning via Multi-Objective Optimization

This dissertation work presents various approaches toward accelerating training of deep neural networks with the use of high-performance computing resources, while balancing learning and systems utilization objectives. Acceleration of machine learning is formulated as a multi-objective optimization problem that seeks to satisfy multiple objectives, based on its respective constraints. In machine learning, the objective is to strive for a model that has high accuracy, while eliminating false positives and generalizing beyond the training set. For systems execution performance, maximizing utilization of the underlying hardware resources within compute and power budgets are constraints that bound the problem. In both scenarios, the search space is combinatorial and contains multiple local minima that in many cases satisfies the global optimum. This dissertation work addresses the search of solutions in both performance tuning and neural network training. Specifically, subgraph matching is proposed to bound the search problem and provide heuristics that guide the solver toward the optimal solution. Mixed precision operations is also proposed for solving systems of linear equations and for training neural networks for image classification for evaluating the stability and robustness of the operations. Use cases are presented with CUDA performance tuning and neural network training, demonstrating the effectiveness

of the proposed technique. The experiments were carried out on single and multinode GPU clusters, and reveals opportunities for further exploration in this critical hardware/software co-design space of accelerated machine learning.

## CURRICULUM VITAE

NAME OF AUTHOR: Robert Lim

## GRADUATE AND UNDERGRADUATE SCHOOLS ATTENDED:

University of Oregon, Eugene, OR, USA University of California, Irvine, Irvine, CA, USA University of California, Los Angeles, Los Angeles, CA, USA

## DEGREES AWARDED:

Doctor of Philosophy, Computer and Information Science, 2021, University of Oregon

Mester of Science, Computer Science, 2014, University of Colifornia, Irvine

Master of Science, Computer Science, 2014, University of California, Irvine Bachelor of Science, Cognitve Science, Specialization in Computing, 2005, University of California, Los Angeles

## AREAS OF SPECIAL INTEREST:

Numerical Analysis Automatic Performance Tuning for GPUs Multi-Objective Optimization High Performance Computing

## PROFESSIONAL EXPERIENCE:

Intern, U.S. Army Engineer Research and Development Center, Geospatial Research Lab, Alexandria, VA

Intern, Université de Versailles, Versailles, France

Mar – Sept, 2019

Intern, Defence Science & Technology Lab, Salisbury, U.K. Aug – Sept, 2017

Intern, The Alan Turing Institute, London, U.K.

June – Aug, 2017

Intern, U.S. Army Engineer Research and Development Center, Geospatial Research Lab, Alexandria, VA

June – Sept, 2016

ASTRO Intern, Oak Ridge National Lab, Oak Ridge, TN

June – Sept, 2014

Extreme Blue Technical Intern, IBM, Austin, TX

May – Aug, 2013

# GRANTS, AWARDS AND HONORS:

| Awards                                                      |                      |

|-------------------------------------------------------------|----------------------|

| Graduate Research Fellowship, University of Oregon          | 2014                 |

| SMART Scholarship Award, U.S. Department of Defense         | 2015                 |

| Chateaubriand Fellowship, Embassy of France in U.S.         | 2017                 |

| Gurdeep Pall Fellowship, University of Oregon               | 2016, 2017           |

| Student Travel Award, Ph.D. Forum                           |                      |

| Supercomputing Conference, Denver, CO                       | Nov 2019             |

| International Conference on Parallel Processing, Eugene, OR | Aug 2018             |

| IEEE Cluster, Chicago, IL                                   | $\mathrm{Aug}\ 2015$ |

| ACM Object-Oriented Programming, Systems, Languages & Ap    | pplications,         |

| Portland, OR                                                | Sept 2014            |

## PUBLICATIONS:

- Lim, R., Oliveira, P., Coti, C., Jalby, W., and Malony, A. "Reduced Precision Computation for Accurate and Robust Learning Systems." 5th Workshop on Naval Applications of Machine Learning, 2021 (poster)

- Lim, R., Norris, B., and Malony, A. "A Similarity Measure for GPU Kernel Subgraph Matching." 31st International Workshop on Languages and Compilers for Parallel Computing, 2019

- Lim, R., Heafield, K., Hoang, H., Briers, M., and Malony, A. "Exploring Hyper-Parameter Optimization for Neural Machine Translation on GPU Architectures." 2nd Workshop on Naval Applications of Machine Learning, 2018

- Lim, R., Norris, B., and Malony, A. "Autotuning GPU Kernels via Static and Predictive Analysis." 46th International Conference on Parallel Processing, 2017

- Lim, R., Norris, B., and Malony, A. "Tuning Heterogeneous Computing Architectures through Integrated Performance Tools." *GPU Technology Conference*, 2016 (poster)

- Lim, R., Malony, A., Norris, B., and Chaimov, N. "Identifying Optimization Opportunities within Kernel Execution in GPU Codes." *International Workshop on Algorithms, Models and Tools for Parallel Computing on Heterogeneous Platforms*, 2015

- Sreepathi, S., Grodowitz, M., Lim, R., Taffet, P., Roth, P., Meredith, J., Lee, S., Li, D., and Vetter, J. "Application Characterization using Oxbow Toolkit and Pads Infrastructure." *International Workshop on Hardware-Software Co-Design for High Performance Computing*, 2014

- Lim, R., Carrillo-Cisneros, D., Alkowaileet, W., and Scherson, I. "Computationally Efficient Multiplexing of Events on Hardware Counters." *Linux Symposium*, 2014

- Alkowaileet, W., Carrillo-Cisneros, D., Lim, R., and Scherson, I. "NUMA-aware Multicore Matrix Multiplication." *Parallel Processing Letters*, 2013

#### ACKNOWLEDGEMENTS

I want to send my sincerest gratitude to the following individuals who have facilitated in the embarkment of this endeavour.

Dissertation committee. Profs. Allen Malony, Boyana Norris, Dejing Dou, Camille Coti, Bill Cresko.

Collaborators. Oak Ridge National Lab: Drs. Jeff Vetter, Megan Grodowitz, Sarat Sreepathi. The Alan Turing Institue: Drs. Kenneth Heafield, Hieu Hoang, Mark Briers. University of Versailles: Drs. William Jalby, Pablo Oliveira.

Compute resources. Argonne National Lab: Drs. Kevin Harms, Phil Carns. NVIDIA: J-C Vasnier, Duncan Poole, Barton Fiske. University of Reims, Champagne Ardenne: Drs. Michael Krajecki, Arnaud Renaud.

Colleagues. TAU Developers: Sameer Shende, Kevin Huck, Wyatt Spear,

Nicholas Chaimov, Aurele Maheo, Josefina Lenis, Alister Johnson, Srinivasan

Ramesh. Office mates: Chad Wood, Daniel Ellsworth, David Ozog. SMART:

Arnold Boedihardjo, Alan Van Nevel, Marisa Garcia, Jessica Holland, Jess Molina,

Brandon Cochenour, Karrin Felton.

University of Oregon. CIS Department: Drs. Joe Sventek, Hank Childs, Reza Rejaie. CIS Staff: Cheri Smith, Jan Saunders, Rob Yelle, Charlotte Wise. Neuroinformatics Center: Dr. Don Tucker, Erik Keever. Division of Graduate Studies: Jered Nagel, Lesley Yates-Pollard, Andy Karduna.

Family members. Mom, Dad, Susa, Melody, Tabitha, Lucas, Chad.

I want to acknowledge my advisor, Prof. Allen Malony, who has undoubtedly created an environment for me to thrive in. That car ride to Falling Sky during my recruitment and the conversation we had about GPUs and harsh

journal reviewers was beyond convincing for me to attend the University of Oregon, not to mention the Eugene mist and Ducks Football. I feel very fortunate for the unconditional advisement I received, having a channel to brainstorm ideas, and plowing through the countless deadlines. I also want to acknowledge my dissertation committee, especially Profs. Boyana Norris and Camille Coti, for their unequivocal support throughout various phases in this process.

Many thanks!

To my dad, whose work ethic has inspired me in many ways.

# TABLE OF CONTENTS

| Cha | apter P.                          | age |

|-----|-----------------------------------|-----|

| I.  | INTRODUCTION                      | 1   |

|     | Overview                          | 1   |

|     | Organization of Dissertation      | 2   |

|     | Background Information            | 2   |

|     | Optimizing Code Generation        | 2   |

|     | GPU Subgraph Matching             | 3   |

|     | Hyper-Parameter Optimization      | 3   |

|     | Numerical Representation          | 4   |

|     | Summary and Future Work           | 4   |

|     | Conclusion                        | 4   |

| II. | BACKGROUND                        | 5   |

|     | Motivation                        | 5   |

|     | Deep Learning Application Domains | 5   |

|     | ML HPC Architectures              | 5   |

|     | Graphic Processing Units          | 6   |

|     | Tensor Processing Unit            | 7   |

|     | Scalable CPUs                     | 8   |

|     | Mixed Precision Numerical Methods | 8   |

|     | AI and HPC                        | 9   |

|     | Background Information            | 9   |

| Cha  | pter                                               | age |

|------|----------------------------------------------------|-----|

|      | Multi-Objective Optimization                       | 10  |

|      | ML Terminology                                     | 11  |

|      | Optimization in Machine Learning                   | 11  |

|      | Stochastic Gradient Descent                        | 13  |

|      | Conclusion                                         | 14  |

| III. | OPTIMIZING CODE GENERATION                         | 15  |

|      | Abstract                                           | 15  |

|      | Motivation                                         | 16  |

|      | Background                                         | 18  |

|      | CUDA Programming Model and Control Flow Divergence | 18  |

|      | GPU Performance Tools                              | 19  |

|      | Autotuning                                         | 19  |

|      | Methodology                                        | 21  |

|      | Occupancy                                          | 22  |

|      | Occupancy Calculation                              | 22  |

|      | Definition of Occupancy                            | 23  |

|      | Theoretical Occupancy                              | 23  |

|      | Instruction Mix Metrics                            | 25  |

|      | Pipeline Utilization                               | 26  |

|      | Infer Kernel Execution Time                        | 27  |

|      | ORIO Code Generation                               | 28  |

|      | OCC Results                                        | 28  |

|      | Environment                                        | 28  |

|      | Discussion                                         | 20  |

| Chapter                                  |   | Page |

|------------------------------------------|---|------|

| Improved Autotuning with Static Analyzer |   | . 32 |

| Related Work                             | • | . 35 |

| Discussion                               |   | . 38 |

| Future Work                              | • | . 38 |

| Conclusion                               | • | . 39 |

| IV. CONTROL FLOW SUBGRAPH MATCHING       | • | . 41 |

| Abstract                                 |   | . 41 |

| Motivation                               |   | . 42 |

| Prior Work                               | • | . 43 |

| Background                               | • | . 45 |

| Kernel Control Flow Graphs               |   | . 46 |

| Transition Probability                   |   | . 48 |

| Hybrid Static and Dynamic Analysis       |   | . 49 |

| Methodology                              |   | . 49 |

| Bilinear Interpolation                   |   | . 50 |

| Pairwise Comparison                      | • | . 50 |

| CFG Results                              |   | . 51 |

| Applications                             | • | . 51 |

| Rodinia                                  |   | . 51 |

| SHOC Benchmark Suite                     |   | . 51 |

| Analysis                                 | • | . 51 |

| Application Level                        | • | . 51 |

| CFG Subgraph Matching                    |   | . 53 |

| Distribution of Matched Pairs            |   | . 53 |

| Cha | apter                                           | Page |

|-----|-------------------------------------------------|------|

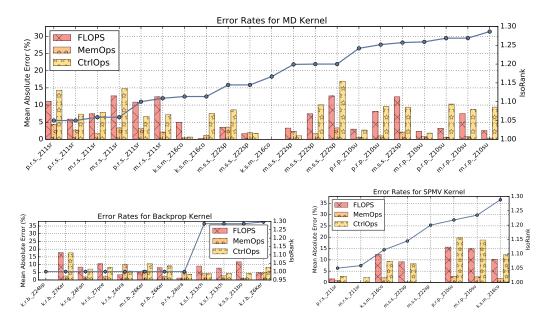

|     | Error Rates from Instruction Mixes              | 54   |

|     | Pairwise Matching of Kernels                    | 56   |

|     | Clustering of Kernels                           | 57   |

|     | Discussion                                      | 58   |

|     | Conclusion                                      | 61   |

| V.  | OPTIMIZING HYPER-PARAMETERS FOR NEURAL NETWORKS | 62   |

|     | Abstract                                        | 62   |

|     | Motivation                                      | 63   |

|     | Related Work                                    | 64   |

|     | Background                                      | 65   |

|     | Machine Translation                             | 66   |

|     | Recurrent Neural Networks                       | 66   |

|     | RNN Encoder-Decoder                             | 67   |

|     | Neural Machine Translation                      | 67   |

|     | Optimization Objectives                         | 68   |

|     | SGD Optimizers                                  | 68   |

|     | Activation Functions                            |      |

|     | Dropout                                         | 70   |

|     | Combination of Optimizers                       | 71   |

|     | Marian NMT                                      | 71   |

|     | Experiments                                     | 72   |

|     | Analysis                                        | 74   |

|     | Translation Quality                             | 74   |

|     | Training Stability                              | 77   |

| Cha  | apter Page                                 | )        |

|------|--------------------------------------------|----------|

|      | Convergence Speed                          | -        |

|      | Cost of Tuning a Hyper-Parameter           | }        |

|      | Summarize Findings                         | Į        |

|      | Discussion                                 | ,<br>)   |

|      | Conclusion                                 | j        |

| VI.  | NUMERICAL REPRESENTATION                   | }        |

|      | Abstract                                   | }        |

|      | Motivation                                 | )        |

|      | Floating-Point Numbers in Machine Learning | )        |

|      | Workflow                                   | )        |

|      | Verificarlo Modes                          | 2        |

|      | Primitive Types from Composite Types       | ŀ        |

|      | Rounding                                   | ó        |

|      | Multi-Objective Optimization               | j        |

|      | Experimental Results                       | 7        |

|      | Applications and Execution Environment     | }        |

|      | Results                                    | )        |

|      | Discussion                                 | }        |

|      | Prior Work                                 | <u>,</u> |

|      | Conclusion                                 | 7        |

| VII. | . SUMMARY AND FUTURE DIRECTIONS            | )        |

|      | Summary                                    | )        |

|      | Future Work                                | )        |

| Chapter | Page                         |

|---------|------------------------------|

|         | Optimizing Code Generation   |

|         | GPU Subgraph Matching        |

|         | Hyper-Parameter Optimization |

|         | Numerical Representation     |

| Sto     | TE FIRST APPENDIX            |

| B. TH   | E SECOND APPENDIX            |

| Bi      | linear Interpolation         |

| Ef      | ficiency and Goodness        |

| REFERE  | NCES CITED                   |

# LIST OF FIGURES

| Figu | ire                                                                                                                                                                              | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

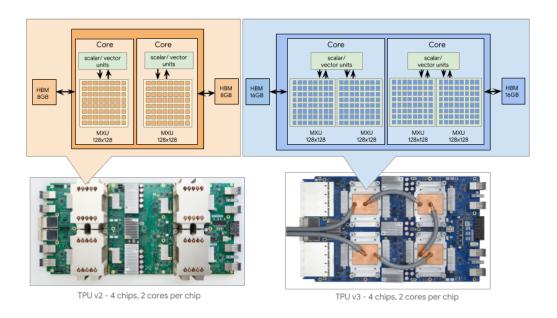

| 1.   | Tensor processing unit (image source Cloud TPU (2019))                                                                                                                           | 7    |

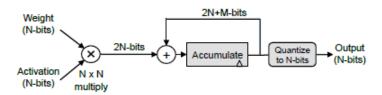

| 2.   | Quantizing multiply-add-accumulate operation                                                                                                                                     | 9    |

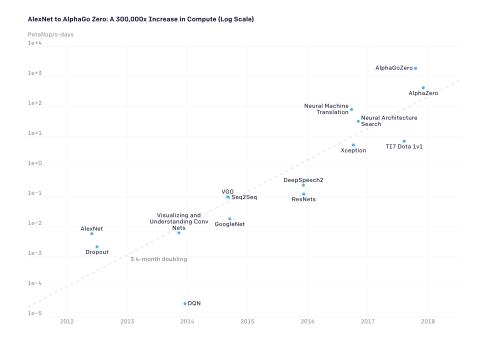

| 3.   | AI training runs, showing 3-4 month doubling time of petaflops. Image source AI and Compute (2018)                                                                               | 10   |

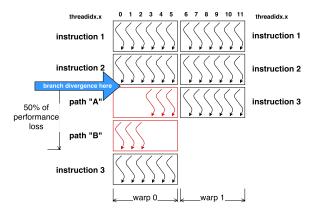

| 4.   | Branch divergence problem and performance loss incurred                                                                                                                          | 18   |

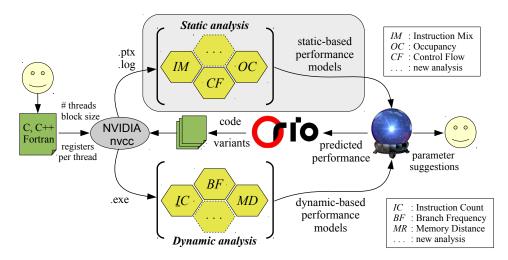

| 5.   | Optimization framework for GPU kernels incorporating static and dynamic analysis, with autotuning and code transformation                                                        | 20   |

| 6.   | Performance autotuning specification                                                                                                                                             | 27   |

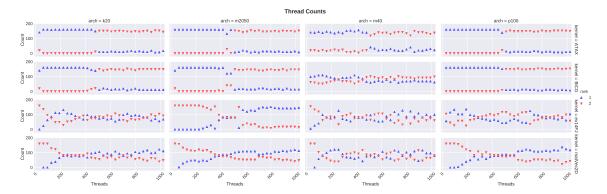

| 7.   | Thread counts for Orio autotuning exhaustive search, comparing architectures and kernels                                                                                         | 29   |

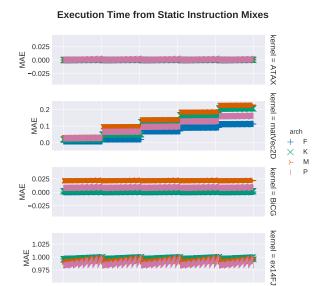

| 8.   | Time-to-instruction mix ratio, comparing architectures and kernels                                                                                                               | 30   |

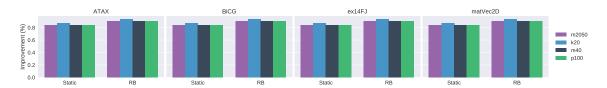

| 9.   | Improved search time over exhaustive autotuning, comparing static and rule-based approaches                                                                                      | 32   |

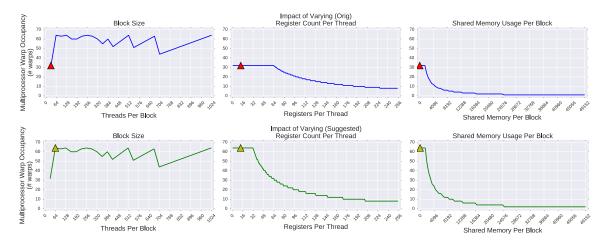

| 10.  | Occupancy calculator displaying thread, register and shared memory impact for current (top) and potential (bottom) thread optimizations for the purposes of increasing occupancy | 36   |

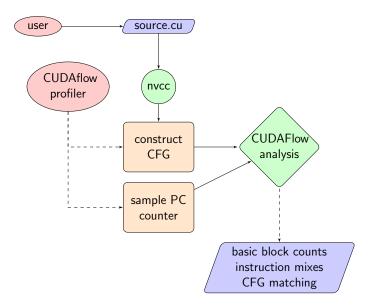

| 11.  | Overview of our proposed CUDAflow methodology                                                                                                                                    | 45   |

|      | · ·                                                                                                                                                                              | 10   |

| 12.  | Control flow graphs generated for each CUDA kernel, comparing architecture families (Kepler, Maxwell, Pascal)                                                                    | 46   |

| 13.  | Transition probability matrices for Pathfinder (dynproc_kernel) application, comparing Kepler (left) and Maxwell (right) versions.                                               | 48   |

| Figu | ire                                                                                                                                                                                                                                                                                                                                                                                  | Page |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

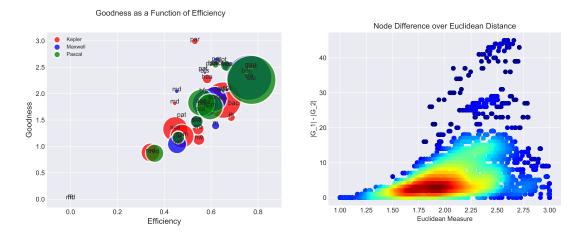

| 14.  | Left: The <i>static</i> goodness metric (Eq. B.2) is positively correlated with the <i>dynamic</i> efficiency metric (Eq. B.1).  The color represents the architecture and the size of bubbles represents the number of operations. Right: Differences in vertices between two graphs, as a function of Euclidean metric for all GPU kernel combinations. Color represents intensity | . 53 |

| 15.  | Error rates when estimating instruction mixes statically from runtime observations for selected matched kernels (x-axis), with IsoRank scores near 1.30                                                                                                                                                                                                                              | . 54 |

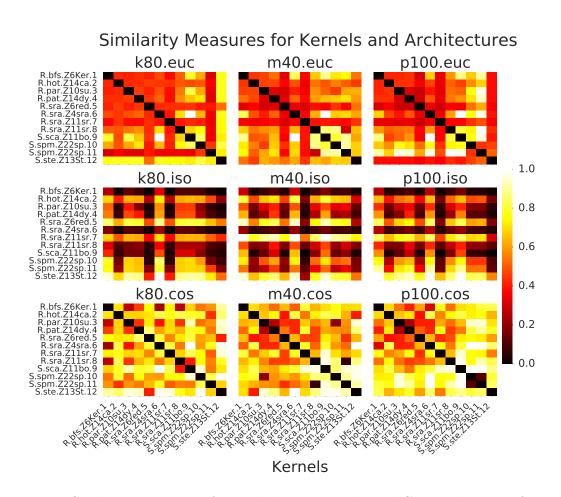

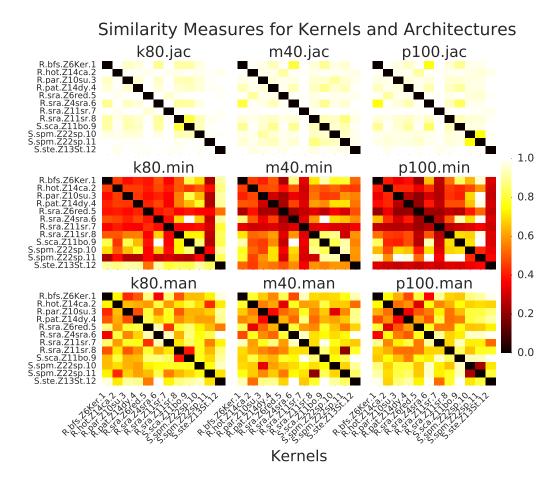

| 16.  | Similarity measures for Euclidean, IsoRank and Cosine distances for 12 arbitarily selected kernels                                                                                                                                                                                                                                                                                   | . 55 |

| 17.  | Similarity measures for Jaccard, Minkowski and Manhattan distances for 12 arbitarily selected kernels                                                                                                                                                                                                                                                                                | . 50 |

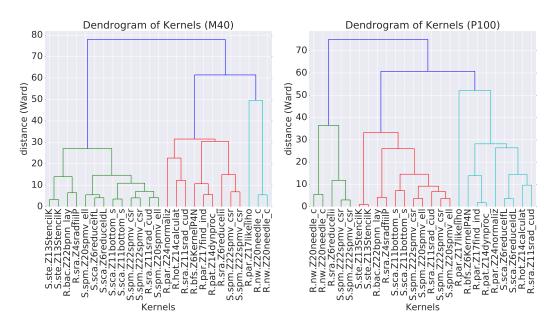

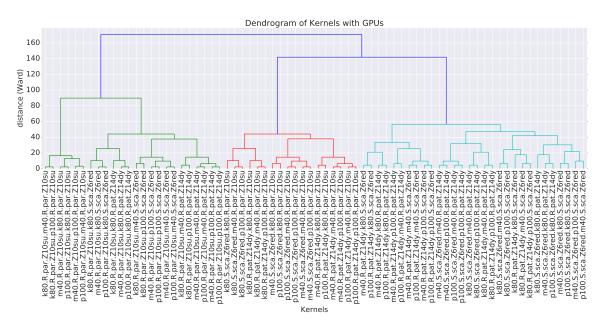

| 18.  | Dendrogram of clusters for 26 kernels, comparing Maxwell (left) and Pascal (right) GPUs                                                                                                                                                                                                                                                                                              | . 57 |

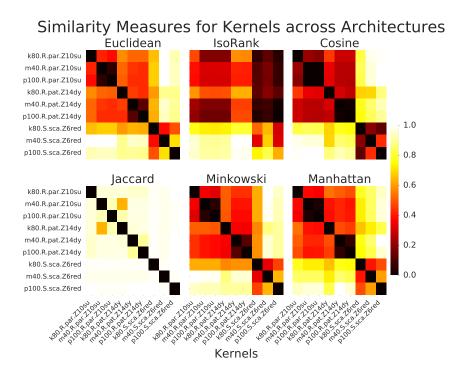

| 19.  | Dendrogram of clusters for pairwise comparison for 3 kernels across 3 GPUs (9 total)                                                                                                                                                                                                                                                                                                 | . 59 |

| 20.  | Dendrogram of clusters for pairwise comparison for 3 kernels across 3 GPUs (27 total)                                                                                                                                                                                                                                                                                                | . 59 |

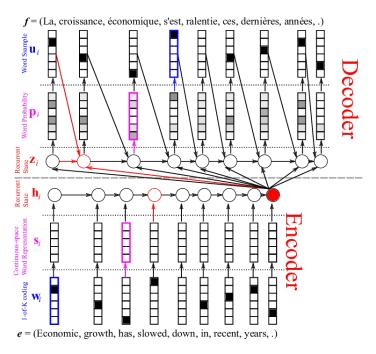

| 21.  | RNN encoder-decoder, illustrating a sentence translation from English to French. The architecture includes a word embedding space, a 1-of-K coding and a recurrent state on both ends. <sup>1</sup>                                                                                                                                                                                  | . 60 |

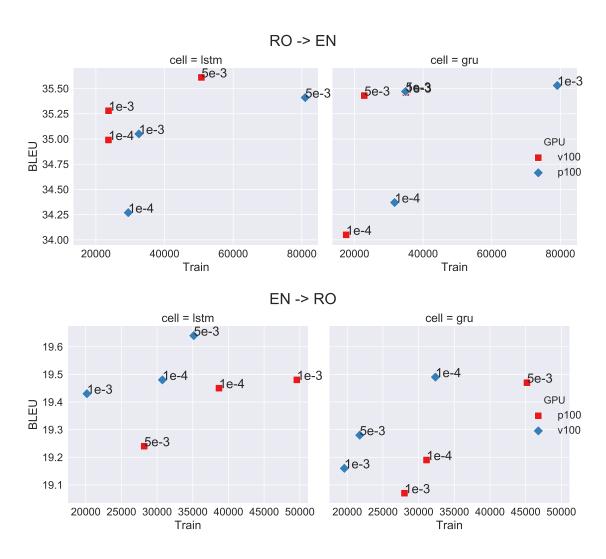

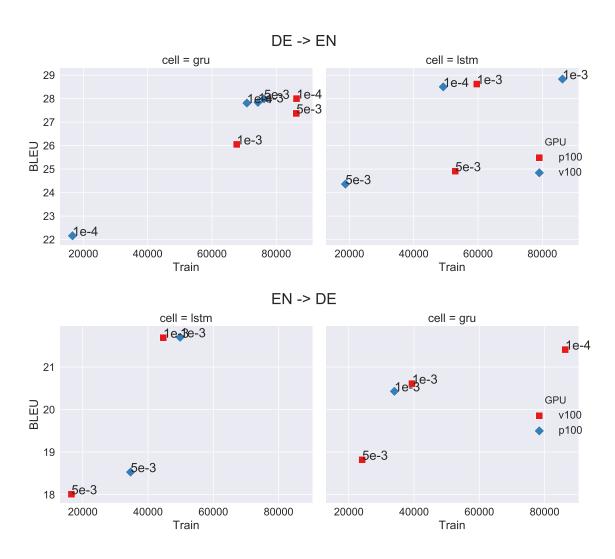

| 22.  | BLEU scores as a function of training time (seconds), comparing GPUs (color), activation units (sub-columns), learning rates and translation directions.                                                                                                                                                                                                                             | . 78 |

| 23.  | BLEU scores as a function of training time (seconds), comparing GPUs (color), activation units (sub-columns), learning rates and translation directions                                                                                                                                                                                                                              | . 79 |

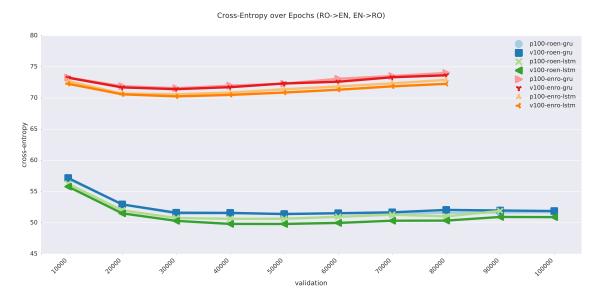

| 24.  | Cross entropy over the number of epochs for RO $\rightarrow$ EN and EN $\rightarrow$ RO, comparing activation functions and GPUs                                                                                                                                                                                                                                                     | . 80 |

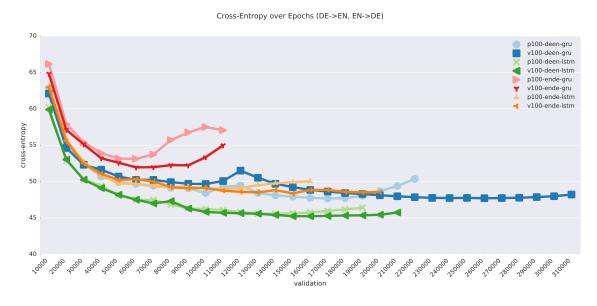

| 25.  | Cross-entropy over the number of epochs for DE $\rightarrow$ EN and EN $\rightarrow$ DE, comparing activation functions and GPUs                                                                                                                                                                                                                                                     | . 80 |

| Figu | re                                                                                                              | Р | age |

|------|-----------------------------------------------------------------------------------------------------------------|---|-----|

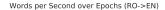

| 26.  | Average words-per-second for the RO $\to$ EN translation task, comparing systems.                               |   | 81  |

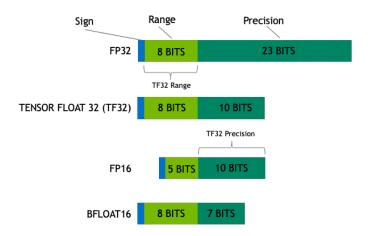

| 27.  | Comparison of floating point representations (image source TF32 (2019a))                                        |   | 89  |

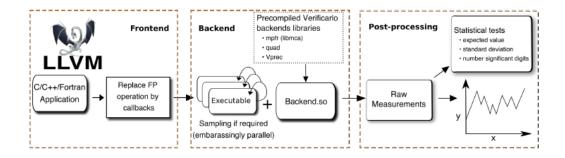

| 28.  | Verificarlo workflow                                                                                            |   | 92  |

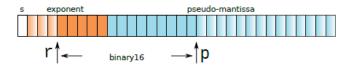

| 29.  | Virtual precision in Verificarlo, showing $r=5$ and $p=10$ , simulating a binary 16 embedded inside a binary 32 |   | 94  |

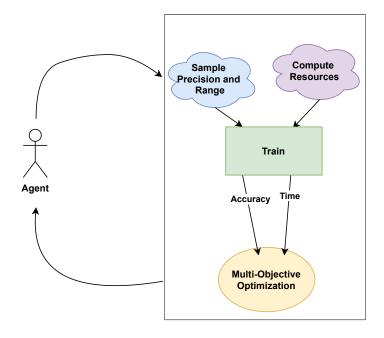

| 30.  | Search for precision and range settings during training                                                         |   | 96  |

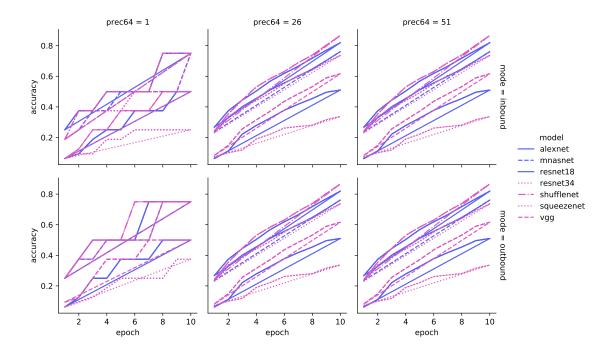

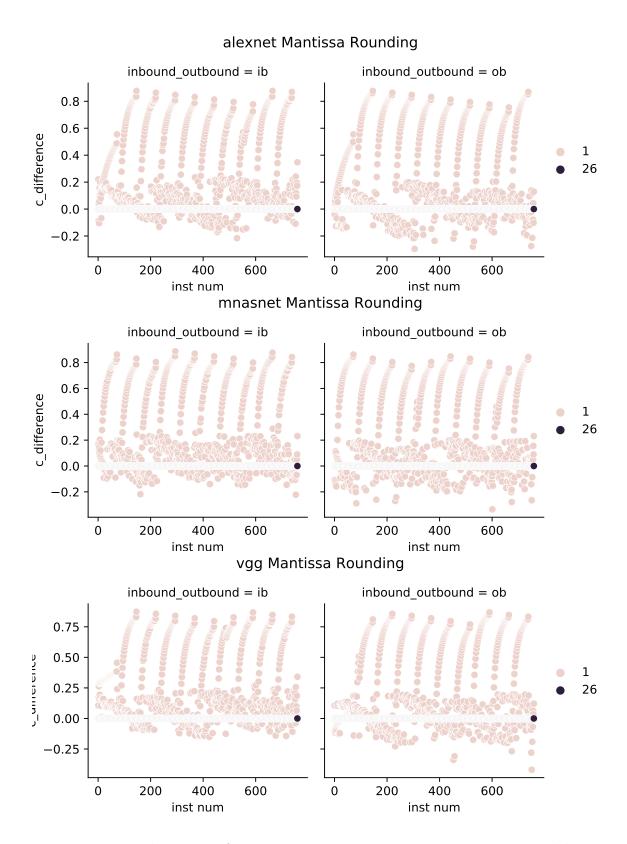

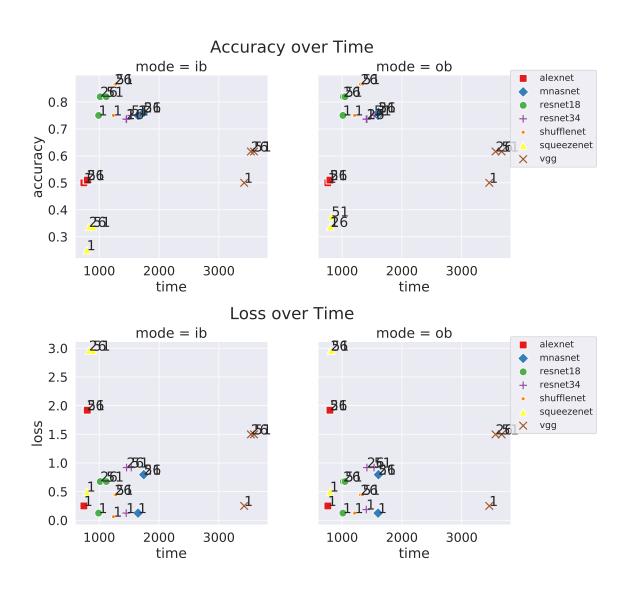

| 31.  | Accuracy per epoch, comparing vision models                                                                     |   | 100 |

| 32.  | Rounding errors for various mantissa sizes, comparing vision models                                             |   | 102 |

| 33.  | Accuracy over time (top) and loss over time (bottom), comparing vision models                                   |   | 104 |

| A.1. | Gradient descent for different learning rates                                                                   |   | 113 |

# LIST OF TABLES

| Tab | ole                                                                                                                                      | Page |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.  | Comparing ML computer processors and accelerators                                                                                        | . 6  |

| 2.  | Selected optimization methods targeting machine learning and high performance computing                                                  | . 12 |

| 3.  | Instruction throughput per number of cycles                                                                                              | . 26 |

| 4.  | A subset of features used for thread block classification                                                                                | . 27 |

| 5.  | Kernel specifications.                                                                                                                   | . 29 |

| 6.  | Statistics for autotuned kernels for top performers (top half) and poor performers (bottom half), comparing GPU architecture generations | . 30 |

| 7.  | Error rates when estimating dynamic instruction mixes from static mixes                                                                  | . 31 |

| 8.  | Suggested parameters to achieve theoretical occupancy                                                                                    | . 33 |

| 9.  | Distance measures considered in this paper                                                                                               | . 50 |

| 10. | Description of SHOC (top) and Rodinia (bottom) benchmarks studied                                                                        | . 52 |

| 11. | Stochastic gradient descent and its variants                                                                                             | . 68 |

| 12. | Activation units for RNN                                                                                                                 | . 69 |

| 13. | Dropout versus a standard update function                                                                                                | . 70 |

| 14. | Marian hyper-parameters, with options in brackets                                                                                        | . 73 |

| 15. | Datasets used in experiments                                                                                                             | . 74 |

| 16. | Graphical processors used in this experiment                                                                                             | . 75 |

| 17. | Hardware and execution environment information                                                                                           | . 75 |

| 18. | BLEU scores for validation (top) and test (bottom) datasets                                                                              | . 76 |

| Tab | le                                                                                                                                                                                        | Р | age |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

| 19. | Dropout rates, BLEU scores and total training time for test set, comparing systems                                                                                                        |   | 76  |

| 20. | Words-per-second (average) and number of epochs, comparing activation units, learning rates and GPUs                                                                                      |   | 82  |

| 21. | Total training time for four translation directions, comparing systems                                                                                                                    |   | 83  |

| 22. | Average time spent per iteration for RO $\rightarrow$ EN and EN $\rightarrow$ RO translation directions, comparing systems, with standard deviation in parenthesis and epochs in brackets | • | 84  |

| 23. | Average time spent per iteration for DE $\rightarrow$ EN and EN $\rightarrow$ DE translation directions, comparing systems, with standard deviation in parenthesis and epochs in brackets | • | 85  |

| 24. | IEEE-754 Numbers and exceptions                                                                                                                                                           |   | 91  |

| 25. | Verificarlo backends and options                                                                                                                                                          |   | 93  |

| 26. | Neural networks for image classification evaluated in this study                                                                                                                          |   | 98  |

| 27. | Intel Xeon Platinum hardware and execution environment information.                                                                                                                       |   | 99  |

| 28. | Statistics for first ten epochs of training, comparing precision sizes and models                                                                                                         |   | 101 |

| 29. | Displaying multi-objective results when accounting for accuracy and average time spent per epoch                                                                                          |   | 103 |

## CHAPTER I

## INTRODUCTION

## Overview

This dissertation work presents various approaches toward accelerating training of deep neural networks with the use of high-performance computing (HPC) resources, while balancing learning and systems utilization objectives. Acceleration of machine learning (ML) is formulated as a multi-objective optimization problem, which seeks to jointly optimize performance and learning objectives, based on its respective constraints. Within each scope, the solver seeks an optimal solution. In machine learning, the solver optimizes a prediction function  $h: \mathcal{X} \to \mathcal{Y}$  from an input space  $\mathcal{X}$  to an output space  $\mathcal{Y}$ , for  $x \in \mathcal{X}$ , such that  $\hat{y} = F_h(x)$  accurately predicts the output and minimizes its empirical risk, defined as the expectation,  $R(F_h) = \mathbb{E}[L(F(h(x)), y)] = \int L(h(x), y) dP(x, y)$ , for some loss function  $L(\hat{y}, y)$  estimating  $\hat{y}$  from y, and the goal is to find  $F_h^*$  $\arg\min_{F_h\in\mathbb{F}}R(F_h)$ , or a prediction function  $F_h^*\in\mathbb{F}$  where  $R(F_h)$  is minimal. When optimizing for execution performance, the solver seeks to minimize a cost function  $g: \mathcal{X} \to \mathcal{Y}$  by selecting the combination of compute resources  $a \in \mathcal{A}$ and transformation options  $o \in \mathcal{O}, \mathcal{X}(\mathcal{A}, \mathcal{O})$ , which yield minimal execution time while maximizing utilization of hardware resources, or  $F_g^* = \arg\min_{F_g \in \mathbb{F}} R(F_g)$ , where  $R(F_g) = \mathbb{E}[F(g(x)), y] = \int L(g(x), y) dP(x, y)$ . Joint optimization of machine learning and high performance computing, discussed in Sec. II, is defined as  $\min_{F_g \in \mathbb{F}} \min_{F_h \in \mathbb{F}} \mathcal{R}(\mathbb{F})$ , for  $F_g, F_h \in \mathbb{F}$ , where  $\mathbb{F}$  represents a vector of objective functions satisfying constraints for its respective domains.

## Organization of Dissertation

This section outlines the dissertation format and provides an overview for each chapter.

Background Information. Accelerating machine learning and multi-objective optimization are presented in Chapter II, which motivates the discussion and provides the background information for the dissertation. The subject matter is on the intersection of high-performance computing and machine learning, specifically how the innovations of heterogeneous parallel programming and methods for analyzing massive amounts of data has transformed industries and society, making this an important field to investigate. Performance optimization depends on numerous elements involved in the computation, including both hardware and software. Thus, the computer architectures, the algorithms, and numerical methods related to machine learning are briefly covered in this chapter.

In the chapters that follow, several approaches are presented for optimizing performance and learning by accelerating the computation kernels used by the machine learning algorithms, by tuning the hyper-parameters of these algorithms, and by understanding the numerical representation of the data handled by these algorithms. The next subsections provide a brief overview and the research questions raised for each chapter.

**Optimizing Code Generation.** Chapter III discusses the work where we proposed metrics for automatic performance tuning of GPU applications. This work seeks to address the following questions:

1. Given the difficult requirements by the user in writing CUDA code, where the user is forced to set threads, blocks, shared memory, and writing efficient

- parallel programs, could we automatically come up with ways that discover optimal parameter settings?

- 2. What metrics can we define statically, such as occupancy, that capture the performance requirements of a computational kernel, and can we use those to help improve our search during automatic performance tuning?

GPU Subgraph Matching. Chapter IV proposes several techniques for performing subgraph matching with GPU kernels. The proposed techniques incorporate the shape and traversal of the graph, its transition probabilities, and hardware information such as the GPU the graph was generated in and instruction mixes. The following questions are proposed:

- 1. Can we come up with compact ways of representing execution performance information of GPU kernels that captures the essence of runtime information, but at the same time, enable us to reason about an unseen kernel's behavior?

- 2. Can we define a similarity metric that enables us to match graphs with one another? This similarity metric needs to be GPU architecture independent, provide a correct measure when measuring with itself, and can match graphs of arbitrary shapes and sizes.

Hyper-Parameter Optimization. Chapter V optimizes hyperparameters for a neural machine translation system. The hyper-parameters explored varies and the study accounts for training stability, trajectories and speed. Other statistics include words processed per second and time to convergence. In this work, we address the following questions:

1. Can we identify which hyper-parameters contribute the most to a model's learning trajectory, while accounting for stability, quality, and speed?

2. Can we identify which hyper-parameters matter most, in terms of system execution performance?

Numerical Representation. Chapter VI examines the numerical requirements when training deep neural networks. In particular, mixed precision operations is proposed that enables users to set the precision and range sizes during training run. The questions raised in this research are the following:

- 1. What are the precision requirements during various iterations of the phase when training deep neural networks?

- 2. Can we propose a dynamic mixed-precision approach toward training neural networks, where the precision sizes can be set during the phase of the training run?

Summary and Future Work. Chapter VII closes by summarizing the work that was discussed in previous chapters and presents areas to pursue for future work.

## Conclusion

An overview of multi-objective optimization and the dissertation format was presented. Next, motivation and background information relating to accelerated machine learning are presented.

#### CHAPTER II

## BACKGROUND

This chapter provides motivation for the dissertation work and covers the basic concepts needed to be discussed further in the dissertation.

#### Motivation

Deep Learning Application Domains. The U.S. Department of Energy has outlined the artifical intelligence (AI) objectives to couple machine learning methods with HPC workloads in its concurrent quest for building the first Exaflop supercomputing machine Stevens et al. (2020). The report identifies areas where ML could augment existing scientific workflows, including chemistry, materials and nanoscience; earth and environmental sciences; biology and life sciences; high energy physics and nuclear physics, amongst others. The nascent social media industry, which provides free services to millions of users, has made billions of dollars deploying deep neural networks to analyze petaflops of user data on-line and off-line for its own use of recommendation systems, computer vision, and language comprehension Park et al. (2018). What makes this innovation possible is both the advancement in AI and the compute infrastructure that delivers instantaneous results to users on their end devices.

ML HPC Architectures. This subsection discusses various computer architectures and accelerators that have been developed for machine learning purposes. Because the majority of operations during machine learning are matrix vector products, much effort has been made to fabricate parallel matrix multipliers to accelerate machine learning. Also referred to as neural processors Neural Processor (2020), these architectures include GPUs, CPUs, and custom ASICs, such as tensor processing units (TPU). Not discussed in this dissertation but also part of

|               | CPU     |          | GPU              |                  | TPU              |                    |

|---------------|---------|----------|------------------|------------------|------------------|--------------------|

|               | Skylake | Cas Lake | Volta            | Ampere           | v2               | v3                 |

| Processor     |         |          |                  |                  |                  |                    |

| Cores         | 28      | 56       | 80               | 96               | 512              | 2048               |

| Freq (MHz)    | 2500    | 2600     | 1328             | 1328             | 700              | 940                |

| Peak Perf     | 2T      | 3.2T     | 125T             | 312T             | 180T             | 420T               |

| Memory        |         |          |                  |                  |                  |                    |

| Type          | DDR4    | DDR4     | HBM2             | HBM2             | HBM              | HBM                |

| Off-chip (GB) | 120     | 140      | 16               | 40               | 32               | 40                 |

| BW (GB/s)     | 16.6    | 23.4     | 900              | 1555             | 2400             | 3600               |

| Hardware      |         |          |                  |                  |                  |                    |

| TDP           | 205     | 400      | 300              | 450              | 280              | 450                |

| MXU           | n/a     | n/a      | $4 \times 4 (8)$ | $4 \times 4$ (4) | $128 \times 128$ | $128\!\times\!128$ |

|               |         |          |                  |                  | (1)              | (2)                |

Table 1. Comparing ML computer processors and accelerators.

neural processors are neuromorphic chips, such as IBM True North Modha (2017) and Intel Loihi Davies et al. (2018), and field programmable gate arrays (FPGA). Table 1, drawn from Wang, Wei, and Brooks (2019); Intel Sky Lake (2017); Intel Cascade Lake (2019), displays a general comparison of CPUs, GPUs and TPUs.

Graphic Processing Units. NVIDIA GPUs, which dominate the market share of accelerators for machine learning due to the proven use of GPUs and the CUDA Deep Neural Network (cuDNN) library, has been aggressively introducing new hardware capabilities for fused operations and reduced precision. Designed originally for real-time graphics rendering using fixed-function pipelines with each pixel performing independent operations in parallel, CUDA debuted as a parallel computing platform in 2007 that enabled user defined programs called shaders that combined the vertex and fragment operations, which is the foundation of the data parallel programming units that run on GPUs and currently

Figure 1. Tensor processing unit (image source Cloud TPU (2019)).

powers some of the world's fastest supercomputers. NVIDIA Volta V100 marks the release of hardware support for tensor cores in 2017 that are capable of executing 4×4 matrices in 16-bit, which uses warps of 32 parallel threads. The NVIDIA Ampere A100, released in 2020, adds the tensorfloat32 instruction set TF32 (2019a), which utilizes 8 bits for the exponent and 10 bits for the mantissa, and is essentially a 19 bit format in a 32 bit register. Software frameworks such as PyTorch, TensorFlow and MxNet rely on the cuDNN library for acceleration. The library can be downloaded for free with a registered NVIDIA account.

Tensor Processing Unit. The tensor processing unit (TPU), created by Google in 2016, is a high-performance, application-specific integrated chip (ASIC) designed for neural network training with 64 GB high-bandwidth memory and 180 teraflops (TFLOPS) peak performance Cloud TPU (2019). Figure 1 displays a schematic representation of the TPUs for v1 and v2. Organized as

a systolic array of 65536 8-bit matrix multiplier units (MXU) with hardwired activation units and a 24 MB unified buffer, inputs are read once and reused, in contrast to the current approach that loads and stores each value TF32 (2019b). Values are further quantized to 8-bits to increase throughput of the instructions. The TPU performs well for training deep neural networks with large batch sizes and is capable of low latency inferencing.

Scalable CPUs. Intel, known traditionally as a CPU manufacturer, has also been agressively wedging in the market share of high-performance computing and machine learning. The CPU's ability for multi-processing with mixed-mode accelerators can be advantageous for AI models, such as reinforcement learning and agent-based modeling. Intel also open sourced the Math Kernel Library Deep Neural Network (MKL-DNN) in 2019 as part of the oneAPI initiative, a unified programming model that targets all Intel devices, including CPUs, GPUs, and FPGAs.

The Intel Xeon Scalable processors enable multi-node multi-socket connection, with 8-bit multiplies and 32-bit accumulates with instructions, such as 8 bit operations accumulated in 16-bit registers (VPMADDUBSW), 16-bit to 32-bit broadcasts (VPMADDWD), and neural network instructions (AVX512\_VNNI), which are 512-bit vectorized intrinsics that perform 8-bit integer operations and accumulates the results to 32-bit registers. Other product lines that Intel provide for AI include Xe GPU accelerators, Arrix FPGAs, and high-performance memory subsystems such as X-point.

Mixed Precision Numerical Methods. Mixed precision algorithms have been successful in providing performance execution benefits, such as increased instruction throughput, less memory footprint and savings in energy. Figure 2

Figure 2. Quantizing multiply-add-accumulate operation.

illustrates how the precision of the output of the activation is reduced to N bits (image source: Sze, Chen, Yang, and Emer (2017)). Reduced precision is commonplace on modern microprocessors and accelerators, such as TPUs that have 8-bit integer arithmetic and GPUs that have mixed precision execution modes, including the Pascal (8-, 16-bit to 32-bit) and the Turing (1-, 4-, 8-, 16-bit to 32-bit) models.

AI and HPC. The advancement of AI has been driven by the algorithmic innovations, massive training sets, and compute capabilities AI and Compute (2018). Figure 3 shows the total amount of compute, in petaflop/s-days, used to train selected AI models. Although one may criticize that the shortcomings of current AI approaches are exposed with the massive compute requirements, the amount of compute availability often facilitates in algorithmic advances, as seen in the evolving AI approaches, from neural networks to reinforcement learning, and the types of problems being solved, including image classification and competitive gaming.

## **Background Information**

This section covers the prerequisite information needed for discussing the dissertation topics. The topics include multi-objective optimization, machine learning terminology, optimization in machine learning, and stochastic gradient descent.

Figure 3. AI training runs, showing 3-4 month doubling time of petaflops. Image source AI and Compute (2018).

Multi-Objective Optimization. Multi-objective optimization seeks to optimize multiple criteria, leveraging overlapping objectives while balancing trade-offs associated with such choices. For accelerating machine learning, multi-objective optimization seeks to achieve quality model learning while leveraging high-performance computing resources.

Multi-objective optimization is formulated as follows. Taken from Miettinen (2012), let k represent the number of objective functions with m inequality constraints and e equality constraints. Let  $\mathbf{x} \in E^n$  be a vector of decision variables with n independent variables,  $x_i$ , and  $\mathbf{F}(x) \in E^k$  be a vector of objective functions,  $F_i(\mathbf{x}) : E^n \to E^1$ , where  $E^1$  represents the criteria, or the cost, of the objective.

Multi-objective optimization is defined as follows:

$$\min_{\mathbf{x}} \mathbf{F}(\mathbf{x}) = [F_1(\mathbf{x}), F_2(\mathbf{x}), ..., F_k(\mathbf{x})]^T$$

subject to

$$g_j(\mathbf{x}) \le 0, j = 1, 2, ..., m,$$

$$h_l(\mathbf{x}) = 0, l = 1, 2..., e.$$

(2.1)

The gradient of  $F_i(\mathbf{x})$  is  $\nabla_{\mathbf{x}} F_i(\mathbf{x}) \in E^n$ , where  $x_i^*$  is a point that minimizes the objective function,  $F_i(\mathbf{x})$ . The feasible design space  $\mathbf{X}$ , or the decision space, is defined as the set  $\{\mathbf{x} \mid g_j(\mathbf{x}) \leq 0, j = 1, 2, ..., m; h_i(\mathbf{x}) = 0, i = 1, 2, ..., e\}$ , whereas the feasible criterion space  $\mathbf{Z}$ , or the attainable set, is defined as  $\{\mathbf{F}(\mathbf{x}) \mid \mathbf{x} \in \mathbf{X}\}$ . Feasiblity implies that no constraints are involved, whereas attainability implies that a point in the criterion space  $\mathbf{Z}$  maps to the decision space  $\mathbf{X}$ . The Pareto optimal is defined as a point  $\mathbf{x}^* \in \mathbf{X}$ , if and only if there does not exist another point, such that  $\mathbf{F}(\mathbf{x}) \leq \mathbf{F}(\mathbf{x}^*)$ , and  $F_i(\mathbf{x}) < F_i(\mathbf{x}^*)$  for at least one criterion.

ML Terminology. Machine learning is a subcategory of artificial intelligence, and neural networks are a subcategory of machine learning that takes a brain-inspired approach toward learning.

Optimization in Machine Learning. Optimization is a mathematical procedure for finding a maximum or a minimum value of a function of several variables, subject to a set of constraints, as in linear programming or systems analysis Chong and Zak (2013). Decision making, where optimization plays a central role, entails selecting the best option amongst a set of alternatives. An objective function, or performance index, provides a "goodness" measure, where the optimization procedure selects the best alternative in light of the given objective function.

Table 2. Selected optimization methods targeting machine learning and high performance computing.

| Algorithmic   | Solver  | Search    | Compilation | Node                   | Distributed    |

|---------------|---------|-----------|-------------|------------------------|----------------|

| SVM           | SGD     | Random    | Loop        | GPU Thread             | Multi-         |

|               |         |           | Transforms  | $\operatorname{Block}$ | $\mathbf{GPU}$ |

| Neural        | Adam    | Grid      | Vector-     | Memory                 | Cluster        |

| Nets          |         |           | /SIMD       | Hierarchy              | Parallelism    |

| Least-squares | Adagrad | Bayesian  | IR          | Intrinsics             | Block          |

|               |         |           |             |                        | Partition      |

| KNN           | FFT     | MCTS      | Mixed       | Operator               | Lazy/Eager     |

|               |         |           | Precision   | Fusion                 |                |

| Reinforcement | Newton  | Heuristic | Kernel      | Rounding               | BFGS,          |

| Learning      |         |           | Fusion      |                        | Downpour       |

Table 2 lists the objectives to optimize for accelerating machine learning. The methods are categorized according to the level of the software stack. Note that this is not an exhaustive list, but a subset that incorporates both ML and HPC. Note, also, that there may be overlaps and that each optimization target may fall under several categories. This dissertation attempts to address the areas that are highlighted.

Algorithmic optimization involves selecting the ML classifier for the task at hand, whether supervised or unsupervised, and its complexity, such as the number of learned parameters. Examples of machine learning algorithms include support vector machines (SVM), neural networks, least-squares methods, K-nearest neighbors (KNN), and reinforcement learning. The solver is the iterative method that provides a performance index during the learning process, and includes stochastic gradient descent (SGD) and its variants, such as AdaGrad and Adam, and second-order methods such as Newton's method, and transformative approaches such as Fast Fourier transform (FFT). Search optimization is concerned with the identification of the maximum or minimum of values. Techniques to

perform search include random, grid, Bayesian, Monte Carlo tree search, and heuristics-based search.

Once the weights have been trained for the model, compilation attempts to optimize the code for execution performance. Code transformations that exploit data locality include loop transformations, vectorization and SIMD approaches, source-to-source translation, reduced precision, and kernel fusion. Single-node optimization targets features available at the computer architecture level, and includes memory hierarchy, intrinsics, and stochastic rounding. Distributed optimization makes use of multiple clusters and multiple accelerators for machine learning, accounting for compute availability, scheduling, checkpointing and problem partitioning. Collectively, this illustrates the complexity and tradeoffs of the landscape when accounting for all factors in optimizing the multiple objectives in machine learning and high-performance computing.

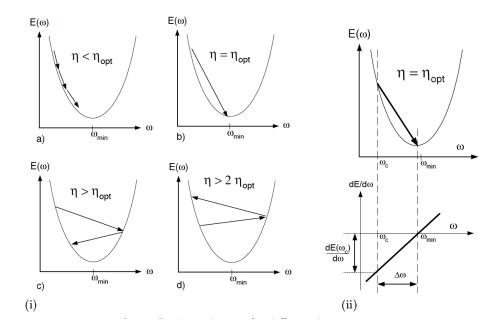

Stochastic Gradient Descent. Stochastic gradient descent is an iterative method that minimizes an objective function F by estimating parameter w for a  $F_i(w)$ , for the i-th observation Stochastic Gradient Descent (2021). For training neural networks, the weights are learned with each batch of data and updated iteratively. Refer to Appendix A for the derivation of stochastic gradient descent.

Algorithm 1 lists the stochastic gradient method, which performs the following steps. A random variable  $\mathcal{E}_k$  is generated via a Taylor expansion series, with  $\{\mathcal{E}_k\}$  representing a sequence of jointly independent random variables. Given an iterate  $w_k \in \mathbb{R}^d$  and the realization of  $\mathcal{E}_k$ , a stochastic vector  $g(w_k, \mathcal{E}_k) \in \mathbb{R}^d$  is computed. Then, given an iteration number  $k \in \mathbb{N}$ , a scalar stepsize  $\alpha_k > 0$  is

## Algorithm 1 Stochastic gradient method.

- 1: Choose an initial iterate  $w_1$

- 2: **for** k = 1, 2, ... **do**

- 3: Generate a realization of the random variable  $\mathcal{E}_k$

- 4: Compute a stochastic vector  $g(w_k, \mathcal{E}_k)$

- 5: Choose a step size  $\alpha_k > 0$

- 6: Set the new iterate as  $w_{k+1} \leftarrow w_k = \alpha_k g(w_k, \mathcal{E}_k)$

computed. The stochastic gradient estimate for g with S samples is defined as

$$\nabla f_{S_k}(w_k; \mathcal{E}_k) = \frac{1}{|S_k|} \sum_{i \in S_k} \nabla f(w_k; \mathcal{E}_{k,i}). \tag{2.2}$$

## Conclusion

This section covered the background information needed to be discussed for the dissertation. Next, we discuss core areas of the dissertation. The core areas of the dissertation include optimizing code generation, control flow subgraph matching, optimizing hyper-parameters, and numerical representation.

#### CHAPTER III

#### OPTIMIZING CODE GENERATION

This chapter includes previously published co-authored material that was published at the 46th International Conference on Parallel Processing Lim, Norris, and Malony (2017). I was the primary contributor to this work in developing the algorithm, writing the new code, and writing the paper. Dr. Boyana Norris initially identified the need for this work and provided the application that this work was performed in. Dr. Allen Malony assisted in editing the paper.

## Abstract

Optimizing the performance of GPU kernels is challenging for both human programmers and code generators. For example, CUDA programmers must set thread and block parameters for a kernel, but might not have the intuition or experience to make a good choice. Similarly, compilers can generate working code, but may miss tuning opportunities by not targeting GPU models or performing code transformations. Although empirical autotuning addresses some of these challenges, it requires extensive experimentation and search for optimal code variants. This research presents an approach for tuning CUDA kernels based on static analysis that considers fine-grained code structure and the specific GPU architectural features. Notably, unlike most autotuning systems, our approach does not require any program runs in order to discover near-optimal parameter settings. We demonstrate the applicability of our approach in enabling code autotuners such as Orio to produce competitive code variants comparable with empirical-based methods, without the high cost of experiments.

#### Motivation

Heterogeneous computing poses several challenges to the application developer. Identifying which parts of an application are parallelizable on a SIMD accelerator and writing efficient data parallel code are the most difficult tasks. For instance, CUDA programmers must set block and thread sizes for application kernels, but might not have the intuition to make a good choice. With NVIDIA GPUs, each streaming multiprocessor (SM) has a finite number of registers, limited shared memory, a maximum number of allowed active blocks, and a maximum number of allowed active threads. Variation in block and thread sizes results in different utilization of these hardware resources. A small block size may not provide enough warps for the scheduler for full GPU utilization, whereas a large block size may lead to more threads competing for registers and shared memory.

Writing kernel functions require setting block and thread parameters, and the difficulty is in deciding which settings will yield the best performance. One procedure entails testing the kernel with block sizes suggested by the CUDA Occupancy Calculator (OCC) CUDA Occupancy Calculator (2016). Although the OCC takes into account the compute capability (NVIDIA virtual architecture) when calculating block sizes and thread counts, inaccuracies may arise because variations in runtime behavior may not be considered, which can potentially result in suboptimal suggested hardware parameters.

How do variations in runtime behavior arise? Accelerator architectures specialize in executing SIMD in lock-step. When branches occur, threads that do not satisfy branch conditions are masked out. If the kernel programmer is unaware of the code structure or the hardware underneath, it will be difficult for them to make an effective decision about thread and block parameters.

CUDA developers face two main challenges, which we aim to alleviate with the approach described in this paper. First, developers must correctly select runtime parameters as discussed above. A developer or user may not have the expertise to decide on parameter settings that will deliver high performance. In this case, one can seek guidance from an optimization advisor. The advisor could consult a performance model based on static analysis of the kernel properties, or possibly use dynamic analysis to investigate alternative configurations. A second concern is whether the kernel implementation is not optimized yet. In this case, advice on parameter settings could still be insufficient because what is really required is a transformation of the kernel code itself to improve performance. For both concerns, static and dynamic analysis techniques are applicable. However, to address the second concern, an autotuning framework based on code transformation is required.

This research presents our static analyzer that can be used by developers, autotuners, and compilers for heterogeneous computing applications. Unlike most existing analysis techniques, our approach does not require any program runs to discover optimal parameter settings. The specific contributions described in this paper include the following.

- A static analyzer for CUDA programs.

- Predictive modeling based on static data.

- Example use cases of the new methodology in an autotuning context.

Figure 4. Branch divergence problem and performance loss incurred.

# Background

This section briefly discusses the background for our research contributions, including the CUDA programming model, performance measurement approaches, and autotuning.

CUDA Programming Model and Control Flow Divergence. In CUDA kernels, threads are organized in groups called blocks, which consist of one or more warps (each of which has 32 threads). Each block is assigned to one of the GPU's streaming multiprocessors, and each SM is composed of multiple streaming processors, or multiprocessors (MP) that execute individual threads in SIMD.

In a given execution cycle, a SM executes instructions from one of the thread block's warps, where threads within a warp are executed together. However, if threads within a warp take different paths on conditional branches, execution of those paths become serialized. In the worst case, only 1 of the 32 threads within a warp will make progress in a cycle. Figure 4 shows how performance is affected when branches diverge. Measuring the occupancy of a kernel execution can determine whether branch divergence exists and suggest parameter adjustments to the program, a subject of this current work.

GPU Performance Tools. To date, GPU performance tools have mainly focused on the measurement and analysis of kernel execution, reporting time and counters associated with kernel execution. For instance, the TAU Performance System provides scalable, profile and trace measurement and analysis for high-performance parallel applications Shende and Malony (2006), including support for CUDA and OpenCL codes Malony et al. (2011). Even though profile measurements can help answer certain types of questions (e.g., how long did foo() take?), improving performance requires more detailed information about the program structure.

While TAU and other profiling tools provide performance measurement Adhianto et al. (2010); ddt (2016); nvprof (2016), they do not shed much light on the divergent branch behavior and its effects on making good decisions about thread and block sizes. Our work introduces several static analysis techniques that deliver fine-grained information that can be used for predictive modeling. These techniques include the ability to analyze instruction mixes and occupancy for estimating thread and register settings. In a complementary approach (not discussed in this paper), we have also developed dynamic analysis techniques to compute instruction execution frequencies and control flow information Lim, Norris, and Malony (2016).

In the remainder of this section, we discuss how we model different performance-relevant metrics by using primarily static analysis of CUDA binaries.

Autotuning. By themselves, performance models can produce adequate predictions of parameter settings, but can not change the kernel to improve performance. Autotuning systems have been important in exploring alternative parameter choices by providing a kernel experimentation and optimization

Figure 5. Optimization framework for GPU kernels incorporating static and dynamic analysis, with autotuning and code transformation.

framework. For example, the open-source Orio autotuning framework Hartono, Norris, and Sadayappan (2009) generates many code variants for each kernel computation. The objective of the GPU portions of Orio is to accelerate loops Chaimov, Norris, and Malony (2014); Mametjanov, Lowell, C.C. Ma, and Norris (2012) since loops consume a large portion of program execution time. We use the term kernels to refer to deeply nested loops that arise frequently in a number of scientific application codes. Existing C loops are annotated with transformation and tuning specifications. Transformations are parameterized with respect to various performance constraints, such as block sizes, thread counts, preferred L1 sizes and loop unroll factors. Each kernel specification generates a family of variant translations for each parameter and each variant is measured for its overall execution time, with the fastest chosen as the top performing autotuned translation.

The main challenge in the optimization space search is the costly empirical measurement of many code variants in autotuning systems. The main contribution

of our work is to demonstrate the use of static predictive models in autotuning, reducing the need for experimental performance testing.

## Methodology

Figure 5 is a high-level depiction of our framework, which illustrates not only the different processes involved, but also the analysis support and tradeoffs inherent in them. For instance, providing a user with runtime parameters for kernel launch could engage static and/or dynamic analysis, but not necessarily code transformation. Dynamic analysis would be expected to be more costly because experiments would be involved. Transforming the implementation allows new variants to be explored, but these could be analyzed either statically or dynamically, or both. However, it is in the integration of these models with an autotuning system that can transform the kernel code where the greatest power for delivering optimizations is found.

## Static Analysis

Our static analysis approach consists of the following steps:

- Extract kernel compilation information with nvcc's --ptxas-options=-v flag.

- 2. Disassemble CUDA binary with nvdisasm for instruction operations executed.

The subsequent sections define metrics resulting from our static analysis approach, including occupancy and instruction mixes. These metrics are then used to significantly reduce or even eliminate the empirical tests in autotuning several kernels.

Occupancy. Threads, registers and shared memory are factors that influence a CUDA kernel's ability to achieve high occupancy. In this section, we will group threads, warps, and blocks into one category for simplifying the discussion, although each term has its own distinct meaning. Threads (T) are the work units performing the computation, whereas warps (W) are the schedulable units for the streaming multiprocessor and blocks (B) consist of groups of warps. Each has memory local to its level. For instance, threads access private registers (R), warps and blocks use shared memory (S), and grids utilize global memory.

The following subsections define factors that contribute to a kernel's GPU occupancy. Table 16 lists the GPUs used in this research, along with hardware features and associated notation. We adopt the naming convention where superscripts denote the source of the variable, with subscripts as constraints of the variable. Compute capability (cc) represents the GPU architecture family (also listed in Tab. 16), meaning nvcc will target an architecture based on the assigned compute capability flag (e.g. -arch=sm\_xx). User input (u) includes threads, registers and shared memory parameters at compile time. Active (\*) represents the results provided by our static analyzer tool. Occupancy is the metric we are calculating and is defined in the next subsections.

Occupancy Calculation. The objective of the occupancy calculation is to minimize the number of active thread blocks per multiprocessor constrained by hardware resource  $\psi$ :

$$B_{mp}^* = \min \left\{ \mathcal{G}_{\psi}(u) \right\}, \tag{3.1}$$

where  $\mathcal{G}(\cdot)$  calculates the maximum allocable blocks for each SM, and  $\psi = \{\psi_W, \psi_R, \psi_S\}$  denotes warps, registers, and shared memory. Each  $\mathcal{G}_{\psi}$  will be defined in Eqs. 3.3, 3.4, and 3.5.

**Definition of Occupancy.** Occupancy is defined as the ratio of active warps on a SM to the maximum number of active warps supported for each SM:

$$occ_{mp} = \frac{W_{mp}^*}{W_{mn}^{cc}} \tag{3.2}$$

where  $W_{mp}^* = B_{mp}^* \times W_B$ , with  $B_{mp}^*$  as defined in Eq. 3.1 and  $W_B = 32$  for all GPUs (Tab. 16). Note that in an ideal world,  $occ_{mp} = 1$ . However, in practice, occupancy rates are on average at 65-75%, and should not be used in isolation for setting CUDA parameters Volkov (2010). Occupancy is one of several metrics we incorporated in our static analyzer.

**Theoretical Occupancy.** The number of blocks which can execute concurrently on an SM is limited by either warps, registers, or shared memory.

Warps per SM The SM has a maximum number of warps that can be active at once. To calculate the maximum number of blocks constrained by warps  $\mathcal{G}_{\psi_W}$ , find the minimum of blocks supported per multiprocessor and the rate of warps per SM and warps per block:

$$\mathcal{G}_{\psi_W}(T^u) = \min\left\{B_{mp}^{cc}, \left| \frac{W_{sm}}{W_B} \right| \right\}$$

(3.3)

where  $W_{sm} = W_{mp}^{cc}$  and  $W_B = \left\lceil \frac{T^u}{T_W^{cc}} \right\rceil$ , with variables as defined in Table 16.

Registers per SM The SM has a set of registers shared by all active threads. Deciding whether registers is limiting occupancy  $\mathcal{G}_{\psi_R}$  is described by the following cases:

$$\mathcal{G}_{\psi_R}(R^u) = \begin{cases}

0 & \text{if } R^u > R_W^{cc}, \\

\left\lceil \frac{R_{sm}}{R_B} \right\rceil \times \left\lceil \frac{R_{fs}^{cc}}{R_B^{cc}} \right\rceil & \text{if } R^u > 0, \\

B_{mp}^{cc} & \text{otherwise.}

\end{cases}$$

(3.4)

where  $R_{sm} = \left\lfloor \frac{R_B^{cc}}{\lceil R^u \times T_W^{cc} \rceil} \right\rfloor$  and  $R_B = \left\lceil \frac{T^u}{T_W^{cc}} \right\rceil$ . Case 1 represents when

the user declares a register value beyond the maximum allowable per thread that is supported for the cc, an illegal operation. Case 2 describes when the user provides a valid register value, where we take the product of the number of registers per SM supported over the number of registers per block and the register file size per MP over the maximum register block supported in this architecture. Case 3 is when the user does not provide a value, where the value is set to the thread block per multiprocessor supported by the cc.

Shared memory per SM Shared memory per thread is defined as the sum of static shared memory, the total size needed for all \_\_shared\_\_ variables and dynamic shared memory. If active blocks are constrained by shared memory, reducing S per T could increase occupancy. To compute  $\mathcal{G}_{\psi_S}$ , take the ceiling of the shared memory per multiprocessor provided by its compute capability over the shared memory per block.

$$\mathcal{G}_{\psi_S}(S^u) = \begin{cases}

0 & \text{if } S^u > S_B^{cc}, \\

\left\lceil \frac{S_{mp}^{cc}}{S_B} \right\rceil & \text{if } S^u > 0, \\

B_{mp}^{cc} & \text{otherwise.}

\end{cases}$$

(3.5)

where shared memory per block  $S_B = \lfloor S^u \rfloor$ , shared memory per SM  $S_{sm} = S_B^{cc}$ , and with cases following similarly to Eq. 3.4.

Instruction Mix Metrics. Instruction mix is defined as the number of specific operations that a processor executes. Instruction mix-based characterizations have been used in a variety of contexts, including to select loop unrolling factors Monsifrot, Bodin, and Quiniou (2002); Stephenson and Amarasinghe (2005), unlike hardware counters which are prone to miscounting events Lim, Carrillo-Cisneros, Alkowaileet, and Scherson (2014). In this work, we use instruction mixes to characterize whether a kernel is memory-bound, compute-bound, or relatively balanced. Refer to Lim, Malony, Norris, and Chaimov (2015) for definitions for  $\mathbf{O}_{fl}$ ,  $\mathbf{O}_{mem}$ ,  $\mathbf{O}_{ctrl}$ , and  $\mathbf{O}_{reg}$  according to category type.

The intensity (magnitude) of a particular metric can suggest optimal block and thread sizes for a kernel. Memory-intensive kernels require a high number of registers, where a large block size consists of more registers per block. The tradeoff with big block sizes is that fewer blocks can be scheduled on the SM. Small block sizes will constrain the number of blocks running on the SM by the physical limit of blocks allowed per SM. Compute-intensive kernels perform well with larger block sizes because the threads will be using GPU cores with fewer memory latencies. Small block sizes will result in many active blocks running on the SM in a time-shared manner, where unnecessary switching of blocks may degrade performance. For control-related synchronization barriers, smaller block sizes are preferred

Table 3. Instruction throughput per number of cycles.

| Category         | Op    | SM20 | SM35 | SM52 | SM60 |

|------------------|-------|------|------|------|------|

| FPIns32          | FLOPS | 32   | 192  | 128  | 64   |

| FPIns64          | FLOPS | 16   | 64   | 4    | 32   |

| CompMinMax       | FLOPS | 32   | 160  | 64   | 32   |

| Shift, Extract,  |       |      |      |      |      |

| Shuffle,         | FLOPS | 16   | 32   | 64   | 32   |

| SumAbsDiff       |       |      |      |      |      |

| Conv64           | FLOPS | 16   | 8    | 4    | 16   |

| Conv32           | FLOPS | 16   | 128  | 32   | 16   |

| LogSinCos        | FLOPS | 4    | 32   | 32   | 16   |

| IntAdd32         | FLOPS | 32   | 160  | 64   | 32   |

| TexIns, LdStIns, | MEM   | 16   | 20   | 6.4  | 16   |

| SurfIns          |       | 16   | 32   | 64   | 10   |

| PredIns, CtrlIns | CTRL  | 16   | 32   | 64   | 16   |

| MoveIns          | CTRL  | 32   | 32   | 32   | 32   |

| Regs             | REG   | 16   | 32   | 32   | 16   |

because many active blocks can run simultaneously on the SM to hide memory latency.

Pipeline Utilization. Each streaming multiprocessor (SM) consists of numerous hardware units that are specialized in performing a specific task. At the chip level, those units provide execution pipelines to which the warp schedulers dispatch instructions. For example, texture units provide the ability to execute texture fetches and perform texture filtering, whereas load/store units fetch and save data to memory. Understanding the utilization of pipelines and its relation to peak performance on target devices helps identify performance bottlenecks in terms of oversubscription of pipelines based on instruction type.

The NVIDIA Kepler GK100 report objdump (2012) lists instruction operations and corresponding pipeline throughputs per cycle. Pipeline utilization describes observed utilization for each pipeline at runtime. High pipeline utilization

```

/*@ begin PerfTuning (

def performance_params {

param TC[] = range(32,1025,32);

param BC[] = range(24,193,24);

param UIF[] = range(1,6);

param PL[] = [16,48];

param SC[] = range(1,6);

param CFLAGS[] = ['', '-use_fast_math'];

}

...

) @*/

```

Figure 6. Performance autotuning specification.

would indicate that the corresponding compute resources were used heavily and kept busy often during the execution of the kernel.

Infer Kernel Execution Time. Because the majority of CUDA applications are accelerated loops, we hypothesize that the execution time of a CUDA program is proportional to the input problem size N. Hence,

$$f(N) = c_f \cdot \mathbf{O}_{fl} + c_m \cdot \mathbf{O}_{mem} + c_b \cdot \mathbf{O}_{ctrl} + c_r \cdot \mathbf{O}_{reg}$$

(3.6)

where  $c_f$ ,  $c_m$ ,  $c_b$ , and  $c_r$  are coefficients that represent the reciprocal of number of instructions that can execute in a cycle, or CPI. Equation 3.6 represents how a program will perform for input size N without running the application.

Table 4. A subset of features used for thread block classification.

| Feature                 | Size                                 |

|-------------------------|--------------------------------------|

| Thread Count            | 32-1024 (with 32 increments)         |

| Block size <sup>1</sup> | 24 – 192 (with 16 increments)        |

| Unroll loop factor      | $\{1-6\}$                            |

| Compiler flags          | <pre>{'', '-use_fast_math'}</pre>    |

| Instructions            | {FLOPS, memory, control}             |

| Occupancy calculation   | {registers, threads, OCC rate, etc.} |